# An MLIR-Based High-Level Synthesis Compiler for Hardware Accelerator Design

A Thesis

SUBMITTED FOR THE DEGREE OF

Doctor of Philosophy

IN THE FACULTY OF ENGINEERING

by

Kingshuk Majumder

Computer Science and Automation Indian Institute of Science  ${\rm BANGALORE} - 560~012$

JANUARY 2023

### ©Kingshuk Majumder JANUARY 2023 All rights reserved

ТО

My parents

### Acknowledgements

I am thankful to my advisor, Uday Bondhugula, for his constant support and guidance. He was always keen to discuss about new ideas and gave me complete freedom in my research direction. He always believed in me through all the tough times during my research. I would also take this opportunity to thank Prof. R Govindarajan, Y.N Srikant and Uday Bondhugula for teaching computer science to an electrical engineer. Without their execellent teaching and support, I would not be able to acquire the necessary skills to complete my Ph.D.

I would like to thank Prateek Jain for giving me the opportunity to work in a world class machine learning team at Google as a student researcher. I would also extend my thanks to my team at Google for all the technically stimulating discussions and for their patience in teaching me the basics of modern machine learning.

I would take this opportunity to thank Prof. Arkaprava Basu for inviting me to his lab's technical discussions and the stimulating conversations. I would like to thank my friends Niladri Das, Daniel Sanju, Narmada Naik, Prateek, Ajay Naik and Shweta Pandey for their support and kindness.

I would conclude by acknowleding the unwaivering support, and countless sacrifices of my parents, Swapan and Madhumita Majumder, without which this work would not have been possible.

#### Vita

Bachelor of Engineering: Electrical Engineering Department Jadavpur University,

West Bengal, India. 2008 - 2012

Master of Engineering: Signal Processing, Electronics and Communication En-

gineering Department, Indian Institute of Science, Ban-

galore, India. 2012 - 2014

Hardware ASIC Engineer: Nvidia, Bangalore, India. 2014 - 2016

Project Associate: Multicore Computing Lab, Department of Computer

Science and Automation, Indian Institute of Science,

Bangalore, India. 2016 - 2017

Student Researcher: Google Research, Bangalore, India. March-Oct 2022

#### Publications based on this Thesis

- 1. Kingshuk Majumder, Uday Bondhugula. Feb-2021. HIR: An MLIR-based Intermediate Representation for Hardware Accelerator Description. [arXiv:2103.00194][code].

- 2. Kingshuk Majumder, Uday Bondhugula. Sep-2022. An ILP-based Automatic Scheduler for High-Level Synthesis of Domain-specific Accelerators [code][Under review].

- 3. Kingshuk Majumder, Uday Bondhugula. Oct-2022. HIR: An MLIR-based Intermediate Representation for Hardware Accelerator Description. [arXiv:2103.00194][code] [Accepted in ASPLOS'24].

#### Abstract

The emergence of machine learning, image and audio processing on edge devices has motivated research towards power-efficient custom hardware accelerators. Though FPGAs are an ideal target for custom accelerators, the difficulty of hardware design and the lack of vendor-agnostic, standardized hardware compilation infrastructure has hindered their adoption. High-level synthesis (HLS) offers a more compiler-centric alternative to the traditional Verilog-based hardware design improving developer productivity.

Though HLS offers many advantages over traditional HDL-based hardware design flow, it is still not a mature ecosystem. There is a need for research in both programming abstraction for hardware design and compiler optimizations to meet the efficiency of hand-optimized HDL designs. In the software world, LLVM has enabled rapid prototyping of programming languages. A new programming language can target the LLVM compiler and benefit from the existing optimizations and backend code generation. LLVM also enables the development of new compiler optimizations. A new optimization pass can be plugged into the existing compiler pipeline to evaluate its benefits on existing programming languages and benchmarks. This decoupling of different stages of the compiler pipeline can be largely attributed to the LLVM intermediate representation.

The high-level synthesis ecosystem still lacks such extensible modular compiler infrastructure which could be used for the development of new HLS programming languages and optimizations. In this work, we propose an MLIR based end-to-end HLS compiler and an intermediate representation that is suitable for the design and implementation of domain-specific accelerators for affine workloads. Our compiler brings similar levels of modularity and extensibility to the HLS compilation domain, which LLVM brought

in the area of software compilation. A modular compiler infrastructure offers the advantage of incrementally introducing new language frontends and optimization passes without the need to reinvent the whole HLS compiler stack.

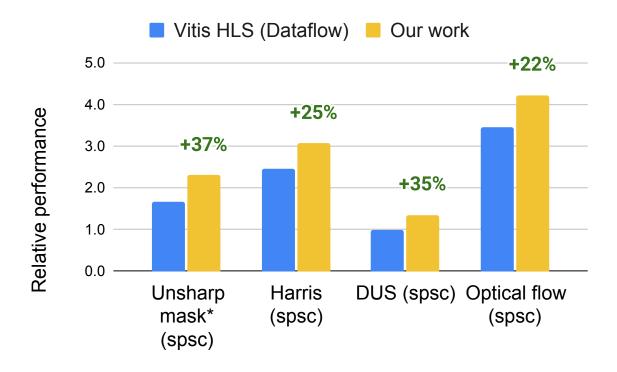

Our compiler converts a high-level description of the accelerator specified in the C programming language into a register-transfer-level(RTL) design (SystemVerilog). We use memory dependence analysis and integer-linear-program(ILP) based automatic scheduling to improve loop pipelining, and introduce parallelization between producer-consumer kernels. Our ILP-based optimizer beats the state-of-the-art Vitis HLS compiler by 1.3x in performance over a representative set of benchmarks, while requiring fewer FPGA resources.

### Contents

| A                | cknov                           | wledge                                              | ements                                                                                                                                                                                                                                                                |      |       | i                                |

|------------------|---------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|

| $\mathbf{V}^{i}$ | ita                             |                                                     |                                                                                                                                                                                                                                                                       |      |       | ii                               |

| Pι               | ıblic                           | ations                                              | based on this Thesis                                                                                                                                                                                                                                                  |      |       | iii                              |

| $\mathbf{A}$     | bstra                           | ct                                                  |                                                                                                                                                                                                                                                                       |      |       | iv                               |

| K                | eywo                            | rds                                                 |                                                                                                                                                                                                                                                                       |      |       | xii                              |

| N                | otati                           | on and                                              | l Abbreviations                                                                                                                                                                                                                                                       |      |       | xiii                             |

| 1                | Intr                            | oduct                                               | ion                                                                                                                                                                                                                                                                   |      |       | 1                                |

| 2                | 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | MLIR<br>Datafi<br>Vitis 1<br>2.4.1                  | ٠                                                                                                                                                                                                                                                                     | <br> | <br>  | 6<br>10<br>13<br>14<br>14<br>17  |

| 3                | 3.1<br>3.2                      | HIR II<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5 | Predictable Representation  Design Time variable and schedules Functions Control Flow Operations Types Undefined Behavior gths of HIR Intermediate Language High-Level Design Explicit Scheduling Deterministic Parallelism External Hardware Modules Predictable QoR | <br> | <br>· | 18 19 20 23 24 25 27 28 29 30 30 |

<u>CONTENTS</u> vii

|   | 3.3  | Expressing Different Types Of Parallelism In HIR    | 0 |

|---|------|-----------------------------------------------------|---|

|   |      | 3.3.1 Instruction Level Parallelism                 | 2 |

|   |      | 3.3.2 Loop Pipelining And Unrolling                 | 2 |

|   |      | 3.3.3 Task Level Parallelism                        | 2 |

|   |      | 3.3.4 Memory Banking And Multi-Port RAMs            | 3 |

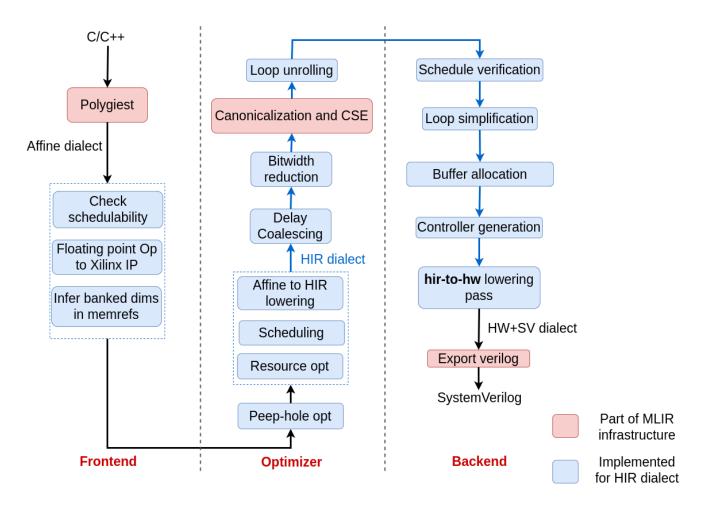

|   | 3.4  | The compiler pipeline                               | 3 |

|   |      | 3.4.1 Polygeist frontend                            | 5 |

|   |      | 3.4.2 Optimizer                                     | 9 |

|   |      | 3.4.3 Schedule verification                         | 3 |

|   |      | 3.4.4 Backend                                       |   |

|   | 3.5  | Summary                                             |   |

| 4 | II D | -Based Automatic Scheduling 4                       | ^ |

| 4 | 4.1  | -Based Automatic Scheduling 4  Correctness Criteria | - |

|   | 4.1  |                                                     |   |

|   |      | S - 1, 1 - 1                                        |   |

|   | 4.3  | ILP Formulation                                     |   |

|   |      | 4.3.1 Intra-Loop Dependence                         |   |

|   |      | 4.3.2 Inter-Loop Dependence                         |   |

|   |      | 4.3.3 Resource Constraints                          |   |

|   |      | 4.3.4 Minimization Objective                        |   |

|   | 4.4  | Summary                                             | 2 |

| 5 | Eva  | luation 6-                                          | 4 |

|   | 5.1  | Evaluation of the HIR Backend                       | 4 |

|   | 5.2  | Evaluation of the Complete HIR Compiler             | 7 |

|   |      | 5.2.1 Results                                       | 1 |

|   | 5.3  | Summary                                             | 7 |

| 6 | Rela | ated work                                           | 9 |

|   | 6.1  | Hardware description languages                      | 9 |

|   | 6.2  | HLS languages & compilers                           | 0 |

|   | 6.3  | DSLs                                                |   |

|   | 6.4  | Source-to-source Compilers                          |   |

|   | 6.5  | Intermediate Representations                        |   |

|   | 6.6  | Place & route for HLS                               |   |

|   | 6.7  | Summary                                             |   |

| 7 | Carr | aclusion 8                                          | ຄ |

| 1 |      |                                                     |   |

|   | 7.1  | Future Work                                         | U |

| A | Sou  | rce code for benchmarks.                            | 3 |

|   | A.1  | Unsharp mask                                        | 3 |

|   | A.2  | Harris                                              | 7 |

|   | A.3  | DUS                                                 | 2 |

| CONTENTS | viii |

|----------|------|

|----------|------|

| A.4 | Optical flow | 104 |

|-----|--------------|-----|

| A.5 | 2mm          | 110 |

### List of Tables

| 5.1 | Description of the handwritten HIR benchmarks for evaluating the back- |    |

|-----|------------------------------------------------------------------------|----|

|     | end                                                                    | 65 |

| 5.2 | FPGA resource usage and comparison with Vitis HLS                      | 65 |

| 5.3 | Resource usage and performance of Vitis HLS and HIR. All designs are   |    |

|     | synthesized at 200MHz. Clock cycles are measured via simulation. Re-   |    |

|     | source usage numbers are post-implementation in Vivado. Vitis HLS can  |    |

|     | not apply dataflow optimizations to 2mm.                               | 70 |

## List of Figures

| 2.1  | Internal design of an FPGA                                                     |

|------|--------------------------------------------------------------------------------|

| 2.2  | Verilog module for the multiply-accumulate operation                           |

| 2.3  | Example of MLIR Affine dialect                                                 |

| 2.4  | Example of a producer and consumer loop nest. The consumer loop can            |

|      | start execution when the producer has written the first two pixels in row      |

|      | <i>R1 of array convX.</i>                                                      |

| 2.5  | Dataflow optimization of Vitis HLS - Vitis HLS adds (a) FIFO to pipeline/over- |

|      | lap within a single function call (improves latency) if the producer and       |

|      | the consumer read the data in the same order. (b) Otherwise, it adds           |

|      | a ping-pong buffer for pipelining between consecutive function calls (im-      |

|      | proves throughput)                                                             |

| 3.1  | Matrix increment and transpose                                                 |

| 3.2  | HIR function definition                                                        |

| 3.3  | Control flow ops in HIR                                                        |

| 3.4  | HIR memref type                                                                |

| 3.5  | Overlapped execution of tasks                                                  |

| 3.6  | Memory banking in a memref type                                                |

| 3.7  | HLS compilation flow                                                           |

| 3.8  | One-dimensional convolution kernel with HLS specific pragmas 37                |

| 3.9  | After preprocessing                                                            |

| 3.10 | After scheduling and lowering to HIR                                           |

| 3.11 | Optimizations after the automatic scheduling                                   |

| 3.12 | Example of a pipeline imbalance                                                |

| 4.1  | Intra-loop memory dependence                                                   |

| 4.2  | Inter-loop memory dependence                                                   |

| 4.3  | Resource-inefficient and -efficient schedules                                  |

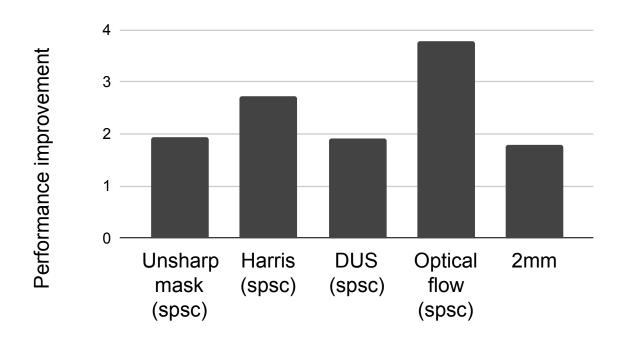

| 5.1  | Performance improvement due to overlapped execution of loop nests 72           |

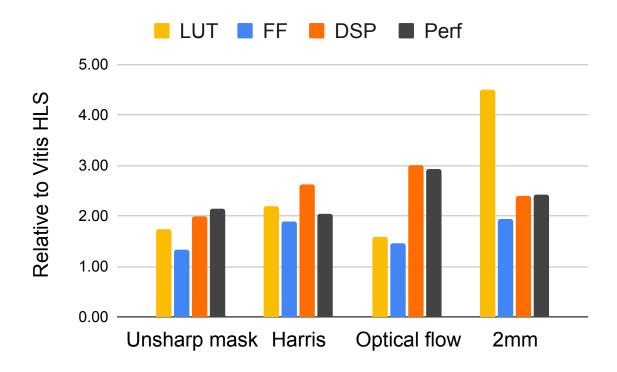

| 5.2  | Performance comparison between Vitis HLS (with dataflow directives) and        |

|      | our work. The baseline is Vitis HLS without dataflow directives                |

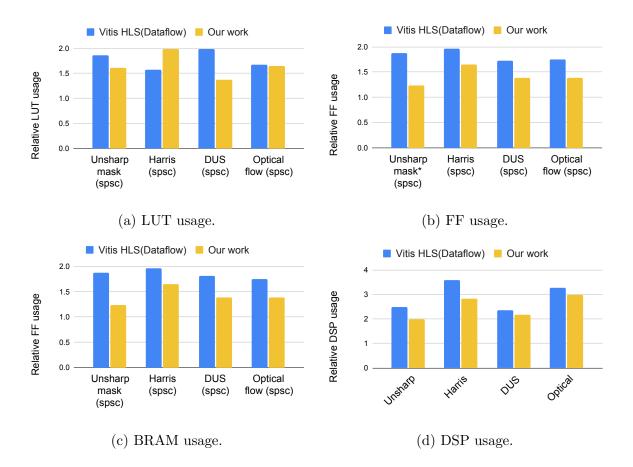

| 5.3  | Resource usage of Vitis HLS with dataflow pragma and our work relative         |

|      | to Vitis HLS without the dataflow directives                                   |

| LIST | $\mathbf{O}\mathbf{E}$ | TITO                     | IDDDC           |

|------|------------------------|--------------------------|-----------------|

| TIST | UГ                     | $\Gamma \perp U \perp U$ | $\mathbf{URES}$ |

|   | • |

|---|---|

| v | 1 |

|   |   |

| 5.4 | Resource usage and performance of our work relative to Vitis HLS for |    |

|-----|----------------------------------------------------------------------|----|

|     | workloads without SPSC dataflow pattern                              | 75 |

|     |                                                                      |    |

### Keywords

MLIR, HIR, HLS, Accelerator, HDL, Verilog, Compiler, Pipelining, Parallelization, CIRCT, ILP.

#### Notation and Abbreviations

BRAM - Block RAM

CGRA - Coarse-Grained Reconfigurable Array

FIFO - First In First Out (Queue)

FMA - Fused Multiply Add FPGA - Field Programmable Gate Array

FSM - Finite State Machine

GLPK - GNU Linear Programming Kit

GPGPU - General Purpose Graphic Processing Unit

HDL - Hardware Description Language

HIR - Hardware Intermediate Representation

HLS - High-Level Synthesis

ILP - Integer Linear Program

IP - Intellectual Property

IR - Intermediate Representation

LUT - Lookup Table

MUX - Multiplexer

MLIR - Multi-Level Intermediate Representation

RAM - Random Access Memory

SPSC - Single Producer Single Consumer

### Chapter 1

#### Introduction

The interest in specialized hardware accelerators has seen a steady rise in the past decade. The growing compute demand for machine learning and image processing in data centers and edge devices, coupled with the need for high energy efficiency, has motivated both industry and academia to explore domain-specific accelerators that can outperform traditional general-purpose compute hardware. To that end, many new accelerators have been proposed by both industry [Jouppi et al. (2017); Choquette et al. (2021); Fricker (2022); Gaide et al. (2019)] and academia [Chen, Yu-Hsin and Krishna, Tushar and Emer, Joel and Sze, Vivienne (2016); Wang et al. (2021); Chen et al. (2014); Kwon et al. (2018); Liu et al. (2015)]. Even General purpose GPUs (GPGPUs), which are designed for efficient execution of highly parallel workloads, introduced specialized accelerators [Markidis et al. (2018)] to address the growing compute demand of machine learning workloads.

Accelerators can optimize the compute and the memory hierarchy to better match the requirements of the workload compared to a general-purpose processor. For instance, both CPUs and GPUs employ hardware-managed caches to capture data reuse. In addition, prefetchers are often used in the hardware to predict complex data access patterns and fetch them to the caches. Prefetchers help in overlapping the compute with the data transfer to/from the memory. This reduces the compute stalls and improves performance. The extra logic required to manage these hardware structures consumes

hardware resources and extra power. On the other hand, accelerators are designed for specific workloads. This simplifies the caching and prefetching mechanisms a lot. Accelerators often use scratchpad memories as software-managed caches and the software/firmware takes care of the prefetching based on the known data access pattern of the target workload. This results in comparable or better data reuse in accelerators while using fewer hardware resources. Similarly, depending on the workload, accelerators may not require special function units (in GPUs) or support for out-of-order execution. All these application-specific optimizations yield more power and area efficient architectures.

Prior work [Chen, Yu-Hsin and Krishna, Tushar and Emer, Joel and Sze, Vivienne (2016)] has shown that different types of on-chip memory accesses can have very different energy costs. Accessing smaller memories such as registers may require an order of magnitude less energy compared to scratchpad memories even though both are on-chip SRAMs. This is attributed to the greater wire length and wider multiplexers for data selection. Systolic arrays are a great example of utilizing this observation to improve power efficiency. The streaming data in a systolic array move from register to register along the width (or height) of the systolic array, reducing the number of scratchpad memory accesses. This improves the power efficiency of the architecture. Such optimizations are not always possible in general-purpose architectures.

With the advantages of these accelerators, comes certain disadvantages as well. Accelerators are not as adaptable as CPUs and GPGPUs. The exact algorithms used for a given workload change/improve over time. For instance, many researchers are trying to improve the performance of machine learning models by exploiting sparsity in the weight and activation matrices. Models are trained to increase sparsity without losing accuracy. These sparsity-related algorithmic improvements do not benefit the actual performance of the neural network if an architecture is not designed to exploit the sparsity and improve memory bandwidth utilization or compute efficiency (by skipping zeroes). CPUs and GPUs require only changes in the software, but accelerators need to be redesigned from scratch to take advantage of these algorithmic advances. In case of ASIC implementations [Jouppi et al. (2017)], designing a new accelerator for modest algorithmic

improvements may not even be an economically feasible approach.

The other disadvantage of accelerators is becoming prominent with the increase in heterogeneity of modern system-on-chips (SOCs). Current generation processors employ dozens of accelerators for different workloads such as image processing, video encoding/decoding, encryption and video compression/decompression. Even though not all the accelerators are used at all times, they consume valuable die area. This partially negates the advantage of area efficiency of custom accelerators over general-purpose architectures.

FPGAs offer an interesting tradeoff between the generality of CPUs and GPUs and the efficiency of custom-designed accelerators. They are more power efficient and have more parallelism than CPUs while being completely reconfigurable. They achieve this at the cost of greater die area and lesser operating frequency compared to an ASIC or CPU. Though FPGAs can never compete in performance or power efficiency with an ASIC, when we factor in the previously discussed issues of adapting to iterative algorithmic improvements and taking advantage of the complete die area in the presence of accelerator heterogeneity, the FPGAs offer a promising alternative. As FPGAs can be reconfigured any number of times, architectures can better adapt to algorithmic improvements. This also incentivizes further research into algorithmic improvements such as increased sparsity, block sparse and low-precision compute. Additionally, different accelerators can time share the whole FPGA instead of statically partitioning the die area among all accelerators.

Custom accelerators on reconfigurable computing platforms such as FPGAs are able to achieve high power efficiency [Zhang et al. (2016)] and performance but the difficulty associated with programming them is seen as a major roadblock towards their mass adoption. High-level synthesis [Canis et al. (2011a)] offers a promising solution towards making custom accelerator design more approachable. DSLs for hardware design can offer an even higher level of abstraction to the algorithm developers and benefit from being able to employ the right high-level synthesis (HLS) pipelines.

Numerous domains-specific as well as general-purpose languages and tools supporting

HLS have been built over the past two decades by the academia and industry [Auerbach et al. (2012); Hegarty et al. (2014, 2016); Reiche et al. (2014); Chugh et al. (2016a); Inc. ([n. d.]); matlab-hdl-coder ([n. d.]); Dase et al. (2006); Najjar et al. (2003); Cong et al. (2011)]. Nearly all electronic design automation vendors now provide suites supporting HLS, examples of which include Xilinx Vivado, Cadence C-to-silicon, Synopsys Synphony, and Mentor Graphics Catapult HLS. A comprehensive survey of various HLS approaches were conducted by Bacon et al. (2013) and Cong et al. (2022).

All these HLS compilers have to create their intermediate representations, thus duplicating and re-implementing a lot of the representation and transformation infrastructure that could otherwise have been shared. Similarly, DSLs [Nigam et al. (2020); Hegarty et al. (2014); Koeplinger et al. (2018); Durst et al. (2020)] either rely on vendor-provided HLS tools or require reimplementing the compiler pipeline, including many standard optimizations, to translate the design into a hardware description language (HDL) like Verilog or Chisel [Bachrach et al. (2012a)].

The problem is even more pronounced while developing new optimizations. Due to lack of a standard compiler infrastructure, any new optimization work [Wang et al. (2021)] has to implement its language frontend and code generator.

The availability of an open IR standard for hardware design would help in decoupling the problem of designing suitable language abstractions for high level synthesis from the problem of optimization and code generation. LLVM [Lattner and Adve (2004)] is a great example of applying this approach to software compilation flow.

In this thesis, we propose the HIR compiler infrastructure and the HIR intermediate representation for high-level synthesis of affine workloads. Affine kernels are present in both image and audio processing as well as machine learning workloads. Often these affine kernels are the performance bottleneck in these workloads. For instance, the majority of the computation in both convolutional neural networks and neural networks for language processing such as transformers are from matrix multiplications. Affine memory accesses also enable the compiler to perform a more precise memory dependence analysis.

The HIR intermediate representation is designed to represent hardware accelerators. It decouples the functional design from the exact schedule giving the compiler greater freedom to choose the implementation for the state-machine-based controller. The IR has a custom data type to represent multi-ported, banked tensors and high-level control flow operations such as loops and if-else statements.

We also implement an ILP-based scheduler for automatic parallelization of the input sequential hardware description in C language. Our scheduler can perform multi-level loop pipelining. It uses the memory dependence analysis to pipeline across producer-consumer loop nests. We also implemented a backend code generator to generate the accelerator in SystemVerilog from the HIR description. Overall, our compiler takes a sequential C implementation of the accelerator with directives for the level of pipelining and parallelism from the programmer and generates a parallel hardware design in SystemVerilog. We have open-sourced the implementation of the HIR compiler [Majumder and Bondhugula (2022)].

The rest of the thesis is organized as follows. In Chapter 2, we provide the necessary background on MLIR, HLS compilers and FPGAs. Chapter 3 introduces the HIR intermediate representation, the optimization passes and the backend. Chapter 4 provides a detailed discussion on our ILP-based automatic scheduler. We evaluate our HLS compiler against Vitis HLS in Chapter 5. We discuss the related work in Chapter 6. Finally, we conclude our thesis in Chapter 7.

### Chapter 2

### Background

In this chapter, we will cover the necessary background for this thesis. Section 2.1 describes the internal design of FPGAs and the challenges in programming them. In Section 2.4, we discuss the Vitis HLS compiler and its dataflow optimization.

#### 2.1 FPGA

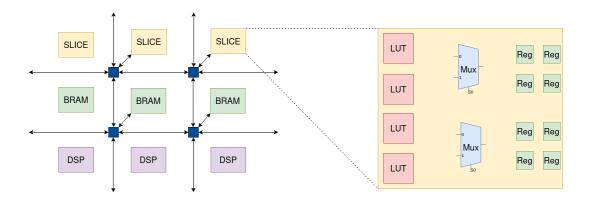

Field programmable gate arrays (FPGAs) are used to implement hardware design. An FPGA contains multiple types of hardware resources such as arithmetic and logic units, block RAMs, registers, multiplexers and lookup tables in a grid. These components are connected via an on-chip reconfigurable network as shown in Figure 2.1. The FPGA can

Figure 2.1: Internal design of an FPGA.

be configured to connect any component to any other component. A hardware design can be implemented on the FPGA by connecting various hardware components using the on-chip network.

The FPGAs differ from CPUs and GPUs in a few important ways. FPGAs do not have any hardware-managed caches. All the on-chip memory is exposed as scratchpad buffers and registers. CPUs and GPUs have a unified address space. Each memory location is associated with a unique address and any part of the program can access any memory location using its address. FPGAs do not have a unified address space. As a result, memory locations do not have a unique global address. In a hardware design, each operation is usually connected to only a subset of the scratchpad memories and can only access these memories. The optimal memory hierarchy is dependent on the dataflow patterns of an application. For instance, certain image-processing applications may require point-to-point communication between functional units [Hegarty et al. (2014, 2016)] and matrix multiplication may require scratchpad memories and registers to capture temporal reuse of the input matrices [Chen, Yu-Hsin and Krishna, Tushar and Emer, Joel and Sze, Vivienne (2016); Jouppi et al. (2017)].

In CPUs and GPUs, the hardware components such as on-chip memory (caches, registers and scratchpad memories), arithmetic and logic units and the on-chip interconnect are abstracted away from the programmer. The instruction set architecture (ISA) exposes a well-defined, and restricted view of the processor internals. As a result, the software can target the CPU/GPU without caring about the internal components. For instance, in modern CPUs, the ISA exposes a set of logical registers. But the number of physical registers available in the processor is far greater than that. The processor internally maps the architectural registers to the physical registers during the program execution. Similarly, many details such as the number of execution cores, the synchronization latency between cores and the size of caches are not exposed as part of the programming model of GPUs. The programmer may use this information to do additional optimizations on the GPU, but it is not required to write correct parallel programs.

FPGAs do not have an instruction set. All the hardware components such as registers,

on-chip memories, arithmetic and logic units, on-chip interconnect and their latencies (number of cycles) are exposed as a part of the FPGA's programming model. A hardware designer needs to specify the exact connection between different hardware components to realize a specific accelerator design.

Since, hardware is inherently parallel, ordering between the execution of different operations must be enforced using state machines. In contrast, each thread in a CPU/GPU program is guaranteed to execute its instructions sequentially. An FPGA design has to schedule different operations in parallel to exploit the instruction level parallelism in the design. CPUs and GPUs also exploit instruction-level parallelism but do not expose it to the programmer. While FPGAs offer fine-grained parallelism, CPU and GPU programs have coarse-grained parallelism in the form of threads.

An FPGA design usually has two components. The datapath specifies how data moves and what operations are performed and how the logic elements are connected to the on-chip buffers. The controller is responsible for specifying the time at which any operation in the datapath is triggered. It is implemented as a finite state machine (FSM).

Another important goal of a hardware design is to achieve a high frequency. Unlike, CPUs and GPUs, the connection between different hardware components is not fixed in an FPGA. As a result, the maximum frequency achieved by an FPGA design depends on which components are connected and on the length of the connecting wires.

Figure 2.2 shows an example of a Verilog module implementing the multiply-accumulate operation. The registers are assigned in an always block. For example, the register a1 is assigned from the wire a. The value in a will propagate to a1 at the next positive edge of the clock. In contrast, the assignment to out from acc3 happens immediately (in the same clock cycle). The whole operation of multiply-accumulate takes 3 cycles. The variables a and b are expected to arrive at the first clock cycle. Input variable c is expected to arrive after one clock cycle delay. Verilog modules do not capture this information about the expected arrival time of each input and the time at which the output is ready. As a result, in a larger design, one multiply-accumulate unit can not be replaced with another unit of different latency even though they are functionally equivalent.

```

module multiply_accumulate(

input wire[31:0] a,

input wire[31:0] b,

input wire[31:0] c,

output wire[31:0] out,

input wire clk

);

reg [31:0] a1;

reg [31:0] b1;

reg [31:0] ab2;

reg [31:0] c2;

reg [31:0] acc3;

always @(posedge clk) begin

a1 <= a;

b1 <= b;

end

wire [31:0] ab = a1 * b1;

always @(posedge clk) begin

ab2 <= ab;

c2 <= c;

end

wire acc = ab2 + c2;

always @(posedge clk) begin

acc3 <= acc;</pre>

end

assign out = acc3;

endmodule

```

Figure 2.2: Verilog module for the multiply-accumulate operation.

#### 2.2 MLIR

In this section, we will provide a background on the MLIR compiler infrastructure [Lattner et al. (2021)]. There are a lot of common building blocks that can be reused across different compilers. Every compiler requires intermediate representations (IR), pass infrastructure for analysis and transformation and printing and parsing support for the IR. Providing a common infrastructure for developing IRs and analysis/transformation passes on these IRs reduces the effort in developing new compilers. MLIR is a compiler infrastructure that can be used to design custom intermediate representations for compilers. It provides a pass infrastructure to develop custom passes of the IR and support for custom parsing and pretty-printing.

An intermediate representation in MLIR is called a dialect. MLIR allows combining multiple dialects in a single program. Figure 2.3 shows an example code snippet in the Affine dialect of MLIR along with some operations from the Func and Arith dialects. An MLIR program consists of operations such as arith.addf in Figure 2.3a. Each operation can have input arguments (%arg2 and %2 for arith.addf operation). Operations can produce one or more results. The input operands and the results are static-single-assignment (SSA) variables, i.e. the variable can not be reassigned. In addition to the input operands, an MLIR operation may have attributes. These attributes provide extra information for the operation. For instance, the constant value of 0 in the arith.constant operation in Figure 2.3a is an attribute. The operation name is always qualified by the dialect name, i.e. the operation arith.constant belongs to the Arith dialect.

Operations can have their own regions. This allows MLIR dialects to have high-level control flow operations. For example, the affine.for operation in Figure 2.3a has one region that contains all the operations in its body. Other operations such as if-else may require multiple regions. Regions are allowed to nest - the func.func operation defines its own region for its body and the affine.for op defines a region nested inside this region.

In addition to custom operations, dialects may define their custom data types. The *memref* type in Figure 2.3a shows an example of a custom data type. The *memref* type is not qualified by a dialect name because it is part of the *builtin* dialect. Types

```

module {

func.func @reduce(%arg0: memref<1024xf32>) -> f32 {

%cst = arith.constant 0.000000e+00 : f32

%0 = affine.for %arg1 = 0 to 10 step 2 iter_args(%arg2 = %cst) -> (f32) {

%1 = affine.load %arg0[%arg1] : memref<1024xf32>

%2 = arith.addf %arg2, %1 : f32

affine.yield %2 : f32

}

return %0 : f32

}

```

(a) Custom pretty printer.

```

map0 = affine_map < (d0) \rightarrow (d0) >

map1 = affine_map < () \rightarrow (0) >

map2 = affine_map < () \rightarrow (10) >

"builtin.module"() ({

"func.func"() ({

^bb0(%arg0: memref <1024xf32>):

\%0 = "arith.constant"() {value = 0.000000e+00 : f32} : () -> f32

%1 = "affine.for"(%0) ({

^bb0(%arg1: index, %arg2: f32):

%2 = "affine.load"(%arg0, %arg1) {map = #map0} : (memref<1024xf32>, index) -> f32

%3 = "arith.addf"(%arg2, %2) : (f32, f32) -> f32

"affine.yield"(%3) : (f32) -> ()

}) {lower_bound = \#map1, step = 2 : index, upper_bound = <math>\#map2} : (f32) -> f32

"func.return"(%1) : (f32) -> ()

}) {function_type = (memref <1024xf32>) -> f32, sym_name = "reduce"} : () -> ()

}) : () -> ()

```

(b) Generic printer.

Figure 2.3: Example of MLIR Affine dialect.

defined in any other dialect are qualified by the dialect name similar to the dialect operations. Types may contain attributes. For instance, the *memref* type stores the tensor dimensions and the element's datatype as attributes.

MLIR provides a generic parser and printer for each dialect. In addition to this, it also provides necessary infrastructure such as lexers and printing/parsing-related helper functions to write custom parsers and printers for each dialect. Dialects may want to define their pretty printing format for improved readability. Figure 2.3b shows the generic printer output for the program in Figure 2.3a. It is easier to understand the input operands and attributes of a function from the generic format. For instance, arith.constant operation has no operands and one attribute named value, and affine.load has two operands (%arg0 and %2) and one attribute named map (an affine-map attribute).

MLIR uses LLVM's tablegen infrastructure to allow defining dialects, operations, types, printers and parsers for the operations and types in a succinct domain-specific language. The tablegen infrastructure generates the necessary class definitions from the tablegen description. Tablegen is also used to define custom passes. A pass recursively visits the operations in the program for analysis and transformation. MLIR also provides pattern-based graph rewriting for simple transformations such as peephole optimization. Many of the MLIR passes can be reused by custom dialects. For instance, dialects can provide custom implementation of certain interfaces for its operations to allow transformation passes such as canonicalization and constant subexpression elimination to run on the dialect operations. This reduces the duplicate effort required to implement these basic passes for each dialect.

Overall MLIR provides a robust infrastructure to develop intermediate representations and compilers. It reduces the programmer's effort by providing many of the common building blocks for compiler development. We built our HLS compiler on top of the MLIR compiler infrastructure.

```

//Producer loop-nest.

for (int i = 0; i < 3; i++) {

convX array

for (int j = 0; j < 3; j++)

(0,2)

#pragma pipeline

convX[0,0] ready

for (int u = 0; u < 2; u++)

(1,2)

#pragma unroll

(2,0) (2,1)

convX[1,1] ready

for (int v = 0; v < 2; v++)

#pragma unroll

convX[i][j] += image[i+u][j+v] * wx[u][v];

//Consumer loop-nest.

The second

for (int i = 0; i < 3; i++) {

convolution

for (int j = 0; j < 3; j++)

can start now.

#pragma pipeline

for (int u = 0; u < 2; u++)

convY[0,0] ready

#pragma unroll

for (int v = 0; v < 2; v++)

#pragma unroll

convY[i][j] += convX[i+u][j+v] * wy[u][v];

intra-loop

convY array

pipelining

```

- (a) Two convolution operations in a series.

- (b) Data dependence & Timing diagram.

Figure 2.4: Example of a producer and consumer loop nest. The consumer loop can start execution when the producer has written the first two pixels in row R1 of array convX.

#### 2.3 Dataflow optimization

Image-processing and machine-learning workloads are often composed of multiple smaller kernels such as convolution and matrix multiplication. For example, the Unsharp mask algorithm contains a series of convolution operations. Machine learning models also often chain multiple window-based (such as convolution or max-pooling) and point-wise (such as RELU) operations together. These tensor operations, represented as a loop nest, may have a producer-consumer relationship among them. Figure 2.4a shows an example of two convolution operations applied on an image successively. The second convolution is dependent on the output of the first convolution. The output of the first convolution loop-nest is written to the convX array by the first loop-nest. The second loop-nest consumes the convX array as input for the second convolution. To improve performance, we unroll the inner two loops and pipeline the j-loop in both convolutions. Figure 2.4b highlights the elements of the array convX that are required to calculate the first element of the convY array. It also shows the timing diagram of iterations of the j-loop. Each iteration of the j-loop is independent of the previous iterations. Thus,

before an iteration of the loop completes, the next iteration can be started as shown in the timing diagram. Overlapping the execution of multiple j-loop iterations improves parallelism. In addition to pipelining between loop iterations (intra-loop pipelining), there is also an opportunity to pipeline between the producer and consumer loop nests (inter-loop pipelining). The second convolution (consumer loop nest) does not have to wait for the first convolution to complete. It can start as soon as enough data is written to the convX matrix to calculate the first convY value. Pipelining between the producer and consumer convolutions overlaps their execution as shown in Figure 2.4b, which further improves parallelism.

#### 2.4 Vitis HLS

Vitis HLS (also known as Vivado HLS) is a high-level synthesis compiler toolchain from Xilinx for their FPGAs. We compare our work against Vitis HLS in this thesis due to its widespread use and maturity. Vitis HLS takes C/C++ as input and generates Verilog as its output. Vitis HLS is built on top of the LLVM infrastructure and utilizes the LLVM IR for many of its optimizations and lowering passes.

The hardware design is expressed as a single-threaded C/C++ program. Vitis HLS supports adding pragmas to control the generated hardware. For instance, there are pragmas for loop unrolling and pipelining. These pragmas help the hardware designer choose the required parallelism and resource usage. An unrolled loop will duplicate the resources (such as multipliers and adders) used inside the loop, but may offer greater parallelism and hence performance. Pragmas are also used to specify the kind of hardware buffers used to realize arrays in hardware - such as block RAMs, ultra RAMs and LUT RAMs.

#### 2.4.1 Limitations of dataflow optimization

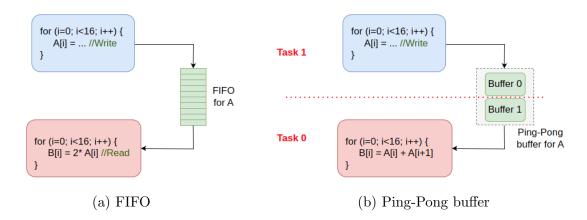

Vitis HLS offers support for both intra-loop pipelining, as well as pipelining across producer-consumer loops. However, the dataflow optimization feature of Vitis HLS for

pipelining the execution of producer-consumer loops within a single function invocation has certain limitations:

- The consumer must read the data in the same order in which the producer generates it.

- Single-producer-single-consumer (SPSC) The intermediate arrays used to communicate between the producer and consumer tasks must have only one producer (i.e., only one task can write to it) and one consumer (only one task can read from it).

- The intermediate arrays must be instantiated in the function itself. Array arguments to a function can not be used to write the intermediate values.

In Figure 2.4a, the single-producer-single-consumer (SPSC) constraint is satisfied since the *intermediate array*, convX, is produced by the first convolution and consumed by the second. However, the second convolution does not read the convX array in the same order in which the first convolution writes to it. In fact, as the consumer task is a stencil operation, the number of reads on convX is more than the number of writes. Due to the abundance of stencil operations in both image processing and machine learning applications, this is a very common scenario.

To understand the reason behind the above limitations dataflow optimization, we first need to discuss how Vitis HLS implements it. For each producer-consumer task pair, Vitis HLS dataflow optimization checks the memory accesses patterns of the intermediate array. If the elements of the intermediate array are read by the consumer in the order in which they are written by the producer, then Vitis HLS can replace the array with a FIFO without altering the program's behavior. The FIFO ensures that the consumer gets the data in the same order in which the producer is generating it. Now, Vitis HLS can start the execution of the consumer loop along with the producer loop without having to worry about data dependence violation. If the producer has not generated and pushed the next value to the FIFO, the consumer automatically stalls while attempting to read that value from the empty FIFO. Thus the read-after-write dependence between

Figure 2.5: Dataflow optimization of Vitis HLS - Vitis HLS adds (a) FIFO to pipeline/overlap within a single function call (improves latency) if the producer and the consumer read the data in the same order. (b) Otherwise, it adds a ping-pong buffer for pipelining between consecutive function calls (improves throughput).

the producer and consumer tasks in the original program is enforced at runtime by the FIFO's synchronization logic. If, in the original program, the order of reads and writes to the intermediate buffer do not match, then Vitis HLS can not replace the intermediate array with a FIFO. In such cases, it instantiates a ping-pong buffer to replace the intermediate array. This optimization helps in pipelining between multiple invocations of the function but does not pipeline between the producer and consumer tasks within a single function invocation. Thus, in the absence of the same read and write order, the dataflow optimization does not improve the overall performance/latency of a single function invocation.

When multiple consumer loops read from the same intermediate array, each consumer loop has to wait unless all other consumers have read the current data before reading the next value. As a result, using a single FIFO with multiple consumers may lead to unexpected stalls, and even deadlock in the presence of additional data dependencies between the consumers. Vitis HLS does not duplicate the FIFOs for multiple consumers. This is probably to ensure that the BRAM usage does not explode after the dataflow optimization. The FIFO-based implementation can not handle multiple producers either since at runtime, two producers running in parallel will insert the data in arbitrary order,

and the consumer will not be able to read the data in the expected order. Due to the above-mentioned limitations of the FIFO-based approach, *dataflow* optimization in Vitis HLS is limited to single-producer-single-consumer (SPSC) workloads.

Similarly, if the intermediate array was accessed via function argument, the optimizer would not have access to the array and would not be able to replace it with a FIFO, leading to the third constraint. This leads to the two hard constraints for dataflow optimization.

Based on the above discussion, we can identify two key attributes of the dataflow optimization,

- Vitis HLS performs a very basic static analysis just to check if the producer and consumer access the intermediate array in the same order. Its static analysis does not handle more complex data access patterns.

- The dataflow optimization relies on runtime synchronization to enforce read-afterwrite dependencies between producer and consumer tasks.

While the lack of better static analysis leads to missed parallelization opportunities for Vitis HLS in the presence of complex memory access patterns, enforcing memory dependence using runtime synchronization can lead to more resource usage. We quantify the effect of these design decisions on the performance and resource usage in Chapter 5.

#### 2.5 Summary

In this chapter, we discussed the necessary background to understand the high-level synthesis compiler landscape. We gave a brief overview of the FPGA internals and discussed the problems associated with designing FPGA accelerators using traditional hardware description language. We also discussed the MLIR compiler infrastructure which we use for developing our own HLS compiler. Finally, we discussed the Vitis HLS compiler and its dataflow optimizations.

### Chapter 3

### HIR Intermediate Representation

An intermediate representation (IR) helps in decoupling the different stages of a compiler pipeline. We need an IR for our compiler that can capture the important properties of a hardware design. A hardware design has three major components, the algorithm, the schedule of computation and the resource binding. Among these, the schedule and the resource binding are unique to a hardware design. The schedule of a computation specifies the time at which each computation is executed. It captures the parallelism in the design and ensures that data dependencies are not violated. The IR must capture a precise schedule after scheduling to synthesize the state machines that control the data path in the hardware design. An FPGA has many different resources such as multipliers, multi-ported block RAMs and registers. For the backend to generate the hardware design, the IR needs to capture the resource binding information, i.e. which resources are used for which operations? For instance, a tensor may be implemented using a single or dual-ported RAM. Similarly, two multiplications scheduled at different clock cycles can reuse the same multiplier.

A single intermediate representation is not suitable at every stage of a compiler pipeline. Transformations at different stages of the compiler pipeline require different levels of abstraction. For instance, certain transformations (such as operator strength reduction) may occur before the scheduling pass. These do not require the scheduling information. Other optimizations such as resource sharing will require a precise schedule

to identify which resources can be reused between two computations. We introduce a new IR called HIR to capture scheduled design with resource-binding information.

In Section 3.1, we discuss the design of the HIR intermediate language in detail. We also discuss various types of undefined behavior in our compiler. We discuss the strengths of HIR in Section . Section 3.3 explains how different types of parallelizations can be captured in HIR. In Section 3.4.2, we discuss the different optimizations applied to an HIR design. Section 3.4.3 discusses the schedule verification pass. Finally, we explain the details of the compiler backend that lowers HIR to SystemVerilog in Section 3.4.4.

#### 3.1 HIR Design

The HIR intermediate representation is implemented as a dialect in the MLIR [Lattner et al. (2021)] compiler infrastructure. As such, it inherits all the usual benefits provided by the core MLIR infrastructure, such as a human-readable textual representation that could be parsed, printed, and verified [Lattner et al. (2020)]. All the HIR operations have a custom pretty-printed form for readability and the convenience of compiler developers. HIR borrows its syntax from software programming languages. Like LLVM, all variables in HIR are SSA variables.

The HIR IR looks very similar to a high-level software IR. It has multi-dimensional arrays and high-level control flow operations such as for/while loops and if-else statements. HIR enhances a software-style IR in two important ways. The first is an abstraction of memory that is suitable for hardware. HIR supports memory banking (mapping a logical memory to multiple physical memories for parallel access) and multi-port RAMs. The second feature that distinguishes it from a software IR is that all HIR designs contain an explicit schedule of all computations. The fine-grained schedule allows the IR to represent different types of parallelism such as instruction-level parallelism, loop pipelining and task-level parallelism. As a part of the MLIR infrastructure, HIR can interoperate with other MLIR dialects. The HIR IR allows arithmetic, logical, slicing and casting operations from hw and comb dialect inside the function body. This allows us to reuse

Figure 3.1: Matrix increment and transpose.

the canonicalization and constant folding function hooks of these operations.

#### 3.1.1 Time variable and schedules

The HIR compiler generates a hardware design with a single clock domain. All operations in the hardware design are synchronized with the positive edge of the hardware clock. This clock provides the notion of time in the hardware design. Each tick (positive edge) of the clock represents a time instant. Each operation in the HIR kernel is called a static instance of the operation. A static instance is uniquely identified by its syntactic position in the kernel. A dynamic instance of an operation is one execution of the operation. A specific operation may execute multiple times during the execution of the kernel. Thus, a static instance of an operation may be associated with multiple dynamic instances. For example, the load operation in line number 16 of Figure 3.1 is a static instance. Since the operation is inside a loop, each iteration of the loop would execute the load operation. Each of these executions of the operation corresponds to a dynamic instance of the operation. Similarly, multiple calls to the enclosing function also lead to multiple dynamic instances for each operation inside the function body. A schedule maps dynamic instances of each operation to a time instant of the clock. The corresponding dynamic instance of the operation is executed at that clock edge. A naive way to define a schedule is to specify the absolute time instant of each operation using an integer. But

this would create a mapping from static instances of the operations to time instants. It does not allow us to map different dynamic instances of the same operation to different time instants.

To solve this problem, we introduce the concept of time-variables. Each region (enclosed in curly braces) in an HIR kernel is associated with a time variable. This time variable represents the time at which the region starts its execution. All operations within the region must execute after this time. A region may be executed multiple times. For instance, a function's body is a region and each call to the function would execute the operations within the region. Thus, just like operations, a single region is also associated with multiple dynamic instances, each corresponding to one execution of the region. For each such dynamic instance of the region, the time variable represents the time instant at which the region started execution. For example, in Figure 3.1, the transpose function defines its start time as %t and the i-loop defines the iteration start time with the time variable %ti. For each function call, the time variable %t would correspond to a different start time. Similarly, for each iteration of the loop within the function call, the time variable %ti would correspond to the start time of the specific iteration within the specific function call. The schedule for each operation within a region is defined as a constant delay from the region's start time. Since the region's start-time for each dynamic execution of the region is different, the dynamic instances of the operations within the region are also mapped to different time instants. In this way, the time variables allow HIR to associate different time instants to different dynamic instances of an operation.

A time variable can be defined in two ways. Each region defines its own start time variable. In Figure 3.1, the function definition operation (hir.func) defines the time variable %t using the at syntax, and the j-loop defines the time variable %tj using the  $iter\_time\ syntax$ . The %t time variable specifies the time at which the function execution starts and %tj specifies the time at which an individual iteration of the j-loop starts. The value of %tj is different for each iteration of the j-loop: %tj = %ti + 1 for iteration (i = 0, j = 0) and %tj = %ti + 2 for iteration (i = 0, j = 1). In addition, loops return a time variable as an output value. This time variable represents the time at which

hir.next\_iter was called in the last loop iteration. The time variable %tf in line number 12 is the time time variable returned by the j-loop. A time variable can be accessed only within the region in which it is defined. Time variables of outer regions are not accessible in the inner regions. For example, %t is not accessible to operations in the i-loop's body. They can only access %ti and %tf time variables defined in the i-loop's body. Similarly, operations in the j-loop's body can only access the %tj time variable.

Time variables are used to schedule the start time of operations. The 'at' keyword represents a use of a time variable except in the function definition. In the function definition, the at keyword defines the time variable to represent the time at which the function starts its execution. In any other operation, the at keyword represents the use of a time variable. The time specified after the at keyword is the time at which the operation is scheduled to start. An optional delay maybe added to a time variable at the use site. For instance, the load and store operations in Figure 3.1 are scheduled to start at time %tj and %tj + 1, where the time variable %tj is defined within the body of the j-loop and represents the start time of each loop iteration.

In addition to operations, all SSA variables of integer and float types are also associated with a time instant. The SSA variables contain a valid value only at the specified time instant. SSA variables of hir.memref type do not have any specific time instant associated with them. Memory elements can be read from or written to at any time instant. Each operation that produces an output value in HIR also specifies the delay from the start of the operation to the time at which the output is available. The SSA variable %u in Figure 3.1 has a valid value at time %tj+1 because the load operation starts at time %tj and it requires a delay of one cycle to load the value from the memory.

The HIR dialect utilizes operations from other MLIR dialects as well. For example, it uses the *comb* dialect for combinatorial operations (operations that complete in the same clock cycle) such as integer arithmetic and logical operations, multiplexing and extracting bit-vectors from larger bit-vectors. This allows us to reuse existing dialect operations and operation-specific canonicalization functions without having to reimplement them for the HIR dialect. To schedule a hardware design, only the operations in the HIR

dialect need to be scheduled explicitly. Since combinatorial operations complete their execution within the same clock cycle, their schedule can be calculated from their input values. For example, in Figure 3.1, the comb.add operation takes %u as input which is valid at time %tj+1. Thus, the comb.add operation is scheduled at the same clock cycle. In addition, the output %v is also produced in the same clock cycle %tj+1. In this way, we can extrapolate the schedule of combinatorial operations from their input values.

The *hir.delay* operation adds a delay of specified clock cycles to the input. As shown in line number 18 of Figure 3.1, the value  $\%j_{-}i4$  is valid at time %tj. It is delayed by one clock cycle to generate the value %j1 which is valid at time %tj+1.

#### 3.1.2 Functions

Figure 3.2: HIR function definition.

Function signatures capture the time at which the input values (of integer and float type) are expected by this function (callee) and the time at which the output values are available to the caller. Figure 3.2 shows the function definition of a multiply-accumulate

operation. The function signature implies that the function starts executing at time instant %t. The inputs %a and %b are read when the function starts. Input %c is read after a delay of three clock cycles i.e., at time %t + 3. The function returns the output after four clock cycles (at %t + 4). Capturing the schedule of function arguments and results enables us to verify the schedule of the complete design without performing an inter-procedural analysis. Analogous to how a function's signature captures sufficient type information for the caller to perform type-checking without inspecting the callee's body, capturing the schedule allows the caller to verify the schedule of operations in its body without analyzing the callee's body. Memory (memref type) arguments specify a list of ports as shown in the *conv* function's signature. The port parameter (captured in the attributes bram\_rw and bram\_rd) specifies the delay in clock cycles associated with each operation. Each port can be a read-only port (ex: bram\_rd), a write-only port or a read-write port (ex: bram\_rw). Function arguments of memref type do not have a delay associated with them because on-chip memory buffers (such as BRAM) are read in multiple clock cycles whereas values can be read in one clock cycle. Thus, we can not associate a single time instant with them.

## 3.1.3 Control Flow Operations

HIR provides multiple primitives to capture the control flow in a design. The HIR compiler automatically synthesizes state machines to implement the control flow.

Figure 3.3 shows the syntax of control flow operations in HIR. The for loop takes a lower bound, an upper bound and a step size. The  $iter\_time$  syntax specifies that the loop starts at the time %t+1. The  $next\_iter$  operation determines the initiation interval of the loop by specifying the start time of the next iteration relative to the current iteration. The for loops in HIR can be either temporal loops (multiple iterations on the same hardware at different times) or spatial loops (loop body unrolled). Since index type represents compile time constant integers in HIR, spatial loops are represented by specifying the loop induction variable as index type.

The if statement takes two input variables. The boolean condition variable (%cond)

```

//%t_end: time at which last iteration calls next_iter.

%t_end = hir.for %i : i32 = %lb to %ub step %c1_i32

iter_time(%ti = %t + 1) {

// The first iteration starts at time %ti=%t + 1,

// Initiation interval is 5 clock cyles.

hir.next_iter at %ti + 5

}

%res = hir.if %cond at time(%t_inner = %t) -> (i1) {

%true_0 = hw.constant true

hir.yield(%true_0) : (i1)

} else {

%false = hw.constant false

hir.yield(%false) : (i1)

}

}

```

Figure 3.3: Control flow ops in HIR.

and a time variable (%t) to represent the time at which the condition is checked. It also defines a new time variable ( $\%t\_inner$ ), which is available inside the then and else bodies to schedule operations inside them.

## 3.1.4 Types

HIR supports primitive data types such as arbitrary bit-width integers and single and double-precision floating-point types. It uses *index* type to represent constant integers and *hir.time* type to represent the type of time variables. In addition to these simple datatypes, HIR defines a container type to represent multidimensional memories in hardware.

All the available memory resources in hardware are represented via the *hir.memref* data type. A *memref* can be viewed as a pointer or reference to a multi-dimensional tensor. The tensor may be placed in an array of buffers (such as distributed or block RAM) or registers. The *memref* type abstracts its implementation details away and provides a uniform interface for memory access.

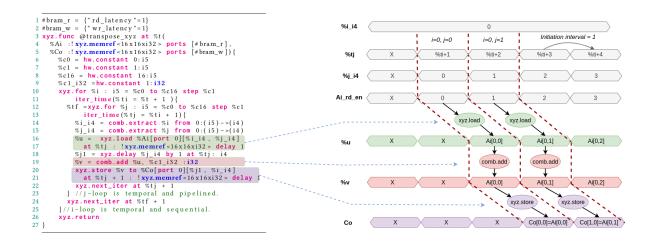

Figure 3.4 shows two alloca operations that allocate new memory elements (block

```

#bram_r = {"rd_latency"=1}

\#bram_w = \{"wr_latency"=1\}

#bram_rw = {"rd_latency"=1, "wr_latency"=1}

\#reg_r = \{"rd_latency"=0\}

\#reg_w = {"wr_latency"=1}

//single port block ram.

%bram_1p = hir.alloca "bram"

: !hir.memref<8x8xi32> ports[#bram_rw]

// simple dual port block ram.

%bram_s2p = hir.alloca "bram"

: !hir.memref<(bank 4)x8xi32> ports[#bram_r, #bram_w]

%reg = hir.alloca "reg"

: !hir.memref<(bank 2)xi8> ports[#reg_r,#reg_w]

//\%0 is of Index type.

\%v = hir.load \%bram_s2p[port 0][\%0, \%i] at \%t

: ! hir.memref<(bank 4) x8xi32>

\label{eq:hir_store} \textbf{hir.store} \ \% \textbf{v} \ \textbf{to} \ \% bram\_1 \textbf{p} [\, \textbf{port} \ 0\, ] [\, \% \, \textbf{i} \, , \, \% \textbf{j} \, ] \ \textbf{at} \ \% \textbf{t} \, + \, 1

: !hir.memref<8x8xi32>

```

Figure 3.4: HIR memref type.

RAMs and registers). The memref datatype defines the dimensions of the tensor, the data type of its elements and memory banking. The ports of the memory are specified using MLIR's dictionary attributes. These attributes (bram\_r, bram\_w) specify the type of the port and the latencies of the read/write operations. If a port attribute specifies both read and write latencies then it is treated as a read/write port with a common address bus. Each port has a dedicated address bus. This approach of representing memory ports gives HIR the flexibility to instantiate memories with an arbitrary number of ports of different types. For example, block RAMs in Xilinx FPGAs are dual ported. A memref can specify separate read and write ports to instantiate a simple dual port RAM or have read+write permission in both ports for a true dual port RAM.

The *memref* can optionally choose to distribute its elements in multiple banks. The dimension(s) to be banked are marked using the *bank* keyword. The banked dimensions

of a *memref* can only be indexed using *index* type which is guaranteed to have a constant value. This ensures that the compiler knows which specific bank is accessed. We discuss the advantages of memory banking in Section 3.3.4. Only one *load/store* operation can be scheduled every cycle for a given port of a bank.

#### 3.1.5 Undefined Behavior

HIR also borrows the concept of undefined behavior from software programming languages. The HIR compiler makes the following assumptions:

- Lower bound of a for-loop is never greater than the upper bound. We use this to simplify the *for-loop* state machine. Also, our scheduler can only handle constant loop bounds, which makes this condition always true.

- A new instance of a for-loop is not scheduled unless the previous instance has completed all iterations. Each instance of a loop requires its loop counter. Since only one counter is instantiated per loop, the hardware can not execute multiple loop instances in parallel. Note that multiple in-flight iterations of a single loop instance, i.e. loop-pipelining, is a perfectly valid optimization.

- There will never be multiple accesses to a *memref* in the same clock cycle unless they occur in different banks or different ports. A memory port has only one address bus. Thus, it can only handle one memory request every cycle. This constraint ensures that there will never be a port conflict in the hardware.

- All load operations happen on initialized memory, i.e., the memory must be written to before reading a value from it. Each call to a function resets all memory elements (such as registers and RAMs) instantiated in the function to an uninitialized state. The HIR language does not support persistent state (equivalent to *static* variables in C) across function calls. Uninitialized memory may have any values, including values from the previous run of the function. We do not zero-initialize buffers on every function call since that would lead to multi-cycle delay overhead for each call.

Thus, a program that reads from uninitialized memory may execute in unexpected ways.

• The timing behavior of external Verilog modules captured in a forward function declaration must match with the implementation. There is no way for the compiler to analyze external Verilog modules. Thus, the compiler relies on the timing information in the function signature (such as when the inputs are expected by the callee and when the output should be ready) to generate correct schedules.

Violation of any of the above assumptions is treated as undefined behavior. optimizers can exploit the undefined behavior to implement more aggressive optimizations that do not violate the semantics. Section 3.4.2 shows one such optimization pass exploits undefined behavior to reduce bitwidth of loop induction variables. All of these undefined behaviors, except the undefined behavior related to external Verilog modules, can be checked during simulation. Our compiler optionally (enabled by a compilation flag) adds extra assertions to check undefined behavior during simulation. This is equivalent to undefined-behavior sanitizers available for languages like C++. These checks improve the functional verification of the final design. We can only perform these checks during the simulation as these assertions are not synthesizable.

# 3.2 Strengths of HIR Intermediate Language

In this section, we discuss the advantages of using HIR as an intermediate language for HLS compilers.

## 3.2.1 High-Level Design

HIR borrows control flow constructs such as loops, function calls and conditional statements directly from imperative programming languages. These features make it easy to convert software algorithms into hardware designs. They also help in representing high-level optimizations such as loop pipelining and overlapped kernel execution.

#### 3.2.2 Explicit Scheduling

Previous work Durst et al. (2020) has shown that statically scheduled designs are more efficient in their hardware utilization since they do not have to implement extra control logic to dynamically communicate between hardware modules. Although such designs are more efficient, the IRs that precisely capture the schedule are usually designed at the abstraction level of hardware description languages. Thus, like HDLs, they require state machines that generate the control signals to determine the order of execution of operations in the data path. Without these control signals, every operation in the hardware will execute every cycle.

Instead of describing a hardware design as datapath + FSM, HIR describes it as datapath + schedule. The hardware design specifies the relative time of execution of each operation and the compiler automatically generates the required FSM. Explicit schedules simplify code generation after automatic scheduling. The scheduling pass does not have to create FSM logic to implement the parallel schedule.

#### 3.2.3 Deterministic Parallelism

Many HLS languages [Nikhil (2004)] and latency insensitive IRs [Nigam et al. (2021)] borrow non-deterministic parallelism from software programming languages. This kind of parallelism often requires a synchronization mechanism. For example, in Vivado HLS a producer and a consumer task can execute in parallel if the producer is transferring its outputs to the consumer via streams (implemented as FIFOs in hardware). This requires handshaking (a form of synchronization) between the producer and consumer. If the two tasks are working in lock-step, i.e., every fixed number of cycles with the producer task generating one output and the consumer task consuming it, then there is no need for synchronization between the two tasks. Both HIR and low-level IRs [Schuiki et al. (2020)] can express this kind of deterministic, synchronization-free, task-level parallelism. Section 3.3.3 shows an example of synchronization-free task-level parallelism.

#### 3.2.4 External Hardware Modules

The ability to use externally defined hardware circuits is essential to specialize a design for the given hardware platform. FPGA vendors provide custom libraries for many common circuits such as floating-point arithmetic and multi-ported RAMs. Additionally, several third-party libraries may need to be reused or inter-operated with.

HIR's ability to capture precise scheduling information in the function signature makes it easier to integrate external Verilog modules with HIR's design. In languages where the schedule is not a part of the language semantics, external modules usually require additional handshake signals. External modules that have fixed latency can interface with HIR without the overhead of handshaking.

#### 3.2.5 Predictable QoR

A predictable quality of result (QoR) is essential for a hardware intermediate representation. This allows DSL/HLS compilers to generate hardware with a predictable performance and resource usage. Control over resource usage is also important when the generated accelerator has to share the FPGA with other Verilog IPs such as PCIe controllers, DRAM controllers and soft CPU cores. An HIR design contains a description of the precise schedule of all operations. Additionally, all resources are explicitly instantiated in the design. Together, these ensure that the performance (amount of parallelism) and resource usage are predictable.

## 3.3 Expressing Different Types Of Parallelism In HIR

HLS compilers are expected to exploit domain knowledge to find potential optimization opportunities [Hegarty et al. (2014)]. A good intermediate language should provide mechanisms to express these optimizations so that the compiler backend can generate the desired circuit. In this section, we discuss various standard hardware optimization techniques and how they can be expressed in HIR.

```

hir.func.extern @stencil_A at %t(

%Ai:!hir.memref<64xi32> ports[#bram_r],

%Bw:!hir.memref<64xi32> ports[#bram_w])

hir.func.extern @stencil_B at %t(

%Br:!hir.memref<64xi32> ports[#bram_r],

%Co:! hir.memref<64xi32> ports[#bram_w])

hir.func @task_parallel at %t(

%Ai :! hir.memref < 64xi32 > ports [#bram_r],

%Co : !hir.memref<64xi32> ports [#bram_w]) {

%B = hir.alloca "bram"

: !hir.memref<64xi32> ports[ #bram_r, #bram_w]

%Br = hir.memref.extract %B[port 0]

: !hir.memref<64xi32> port[ #bram_r]

%Bw = hir.memref.extract %B[port 1]

: !hir.memref<64xi32> port [ #bram_w]

// Execution of stencilB is overlapped with stencilA.

hir.call @stencil_A(%Ai, %Bw) at %t

: !hir.func <(!hir.memref < 64xi32 > ports [#bram_r],

!hir.memref<64xi32> ports[#bram_w])>

hir.call @stencil_B(%Br, %Co) at %t + 8

: !hir.func <(!hir.memref < 64xi32 > ports [#bram_r],

!hir.memref<64xi32> ports [#bram_w])>

hir.return

```

Figure 3.5: Overlapped execution of tasks.

#### 3.3.1 Instruction Level Parallelism

The HIR IR can capture fine-grained instruction-level parallelism. For instance, multiple independent operations can be scheduled at the same time to improve parallelism. Similarly, operator chaining can be used to schedule multiple dependent operations in the same clock cycle, which would otherwise span multiple cycles. In case multiple dependent operations can not be scheduled at the same cycle to meet frequency targets, pipeline registers can be added between instructions. An HIR design uses *hir.delay* operation to add pipeline registers between dependent operations.

### 3.3.2 Loop Pipelining And Unrolling

Loop pipelining is a key optimization in high-level synthesis. In loop pipelining, the next iteration of the for loop starts before the previous iteration completes. This allows multiple loop iterations to execute in parallel. Loop pipelining does not add extra hardware overhead. A *for* loop with a constant initiation interval is shown in Figure 3.3.

Unrolling replicates the loop body in hardware. This allows an HIR design to scale with available hardware resources if there is enough loop parallelism. Unrolling can often be combined with pipelining to further improve parallelism. A loop where the induction variable is of *Index* type is unrolled fully. HIR does not support the partial unrolling of loops. Partial unrolling can be represented by strip-mining the *for* loop and completely unrolling the resultant inner loop.

#### 3.3.3 Task Level Parallelism

In addition to exploiting parallelism in loops, multiple tasks can be executed in parallel to further improve performance. The "task\_parallel" function in Figure 3.5 shows an example of task-level parallelism expressed in the HIR dialect. Since the stencils read the input array and write to the output sequentially, the second stencil does not have to wait for the first stencil to complete. It can start its operation as soon as there is enough data to calculate its first output. After that both the stencil run in lock steps i.e. in each cycle

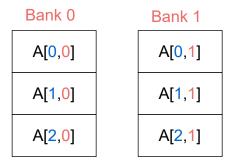

A is of type hir.memref< 3 x (bank 2) x i32>