# Automatic Data Allocation, Buffer Management and Data Movement for Multi-GPU Machines

#### A Thesis

SUBMITTED FOR THE DEGREE OF

Master of Science (Engineering)

IN THE COMPUTER SCIENCE AND ENGINEERING

by

Thejas Ramashekar

Computer Science and Automation Indian Institute of Science BANGALORE – 560 012

OCTOBER 2013

i

©Thejas Ramashekar OCTOBER 2013 All rights reserved

### Acknowledgements

I take this opportunity to thank all those who made this thesis work possible. First and foremost, I thank my advisor Dr. Uday Bondhugula for his invaluable guidance. He helped us to get started by guiding us thoroughly through our first joint work, out of which I found the motivation and the necessary expertise for the main problem solved in the thesis. He gave me enormous amount of freedom in selecting the problem and approaching the solution and was always there with a timely guidance when I needed it.

I specially thank the members of the Multi-core Computing Lab who made the day-to-day environment both academically and otherwise refreshing. Without them, the lab would not have been the wonderful workplace that it is. Special thanks to Roshan Dathathri for being always enthusiastically available for a technical discussion and his help towards reviews and suggestions. I would like to thank my friend Jay Thakkar for all his help with Tikz diagrams used in this thesis.

I would also like to specially thank my wife Pallavi for her constant support during times of need, sharing in my happiness during times of joy, and timely warnings whenever I slacked in my work.

I have been fortunate to have a enviable group of close friends whose support and company made the entire experience a truly memorable one.

Finally, I would like to thank my parents, and sister for their support and encouragement without which I would not have even thought of pursuing higher education.

### Publications based on this Thesis

- Thejas Ramashekar, Uday Bondhugula, Automatic Data Allocation and Buffer Management for Multi-GPU machines. In the ACM Transactions on Architecture and Code Optimization, Vol. 10, No. 4, Article 60, Publication date: December 2013. Selected for presentation at HiPEAC 2014, Jan 2014, Vienna, Austria.

- 2. Roshan Dathathri, Chandan Reddy, Thejas Ramashekar, and Uday Bondhugula. Generating efficient data movement code for heterogeneous architectures with distributed-memory. In the 22nd International Conference on Parallel Architectures and Compilation Techniques (ACM/IEEE PACT), September 2013, Edinburgh, Scotland.

### Abstract

Multi-GPU machines are being increasingly used in high performance computing. These machines are being used both as standalone workstations to run computations on medium to large data sizes (tens of gigabytes) and as a node in a CPU-MultiGPU cluster handling very large data sizes (hundreds of gigabytes to a few terabytes). Each GPU in such a machine has its own memory and does not share the address space either with the host CPU or other GPUs. Hence, applications utilizing multiple GPUs have to manually allocate and manage data on each GPU.

A significant body of scientific applications that utilize multi-GPU machines contain computations inside affine loop nests, i.e., loop nests that have affine bounds and affine array access functions. These include stencils, linear-algebra kernels, dynamic programming codes and data-mining applications. Data allocation, buffer management, and coherency handling are critical steps that need to be performed to run affine applications on multi-GPU machines. Existing works that propose to automate these steps have limitations and inefficiencies in terms of allocation sizes, exploiting reuse, transfer costs and scalability. An automatic multi-GPU memory manager that can overcome these limitations and enable applications to achieve scalable performance is highly desired.

One technique that has been used in certain memory management contexts in the literature is that of *bounding boxes*. The bounding box of an array, for a given tile, is the smallest hyper-rectangle that encapsulates all the array elements accessed by that tile. In this thesis, we exploit the potential of bounding boxes for memory management far beyond their current usage in the literature.

In this thesis, we propose a scalable and fully automatic data allocation and buffer

management scheme for affine loop nests on multi-GPU machines. We call it the Bounding Box based Memory Manager (BBMM). BBMM is a compiler-assisted runtime memory manager. At compile time, it uses static analysis techniques to identify a set of bounding boxes accessed by a computation tile. At runtime, it uses the bounding box set operations such as union, intersection, difference, finding subset and superset relation to compute a set of disjoint bounding boxes from the set of bounding boxes identified at compile time. It also exploits the architectural capability provided by GPUs to perform fast transfers of rectangular (strided) regions of memory and hence performs all data transfers in terms of bounding boxes. BBMM uses these techniques to automatically allocate, and manage data required by applications (suitably tiled and parallelized for GPUs). This allows it to (1) allocate only as much data (or close to) as is required by computations running on each GPU, (2) efficiently track buffer allocations and hence, maximize data reuse across tiles and minimize the data transfer overhead, (3) and as a result, enable applications to maximize the utilization of the combined memory on multi-GPU machines. BBMM can work with any choice of parallelizing transformations, computation placement, and scheduling schemes, whether static or dynamic. Experiments run on a system with four GPUs with various scientific programs showed that BBMM is able to reduce data allocations on each GPU by up to 75% compared to current allocation schemes, yield at least 88% of the performance of hand-optimized OpenCL codes and allows excellent weak scaling.

### Contents

| A            | ckno  | wledgements                                                           | j          |

|--------------|-------|-----------------------------------------------------------------------|------------|

| P            | ublic | ations based on this Thesis                                           | ii         |

| $\mathbf{A}$ | bstra | ct                                                                    | iii        |

| Li           | st of | Figures                                                               | ix         |

| Li           | st of | Algorithms                                                            | x          |

| 1            | Intr  | roduction                                                             | 1          |

|              | 1.1   | GPUs in high performance computing                                    | 1          |

|              | 1.2   | Towards Multi-GPU machines                                            | 2          |

|              | 1.3   | Programming challenges on a multi-GPU machine                         | 3          |

|              |       | 1.3.1 Computation partitioning and load balancing                     | 3          |

|              |       | 1.3.2 Data allocation and buffer management                           | 3          |

|              |       | 1.3.3 Inter-GPU data movement                                         | 4          |

|              |       | 1.3.4 Existing approaches                                             | 4          |

|              | 1.4   | Affine loop nests                                                     | 5          |

|              |       | 1.4.1 Running affine loop nests on multi-GPU machine                  | 5          |

|              | 1.5   | Need for a multi-GPU memory manager                                   | 5          |

|              |       | 1.5.1 Desired capabilities                                            | 6          |

|              | 1.6   | Bounding Box based Memory Manager                                     | 7          |

|              | 1.7   | Contributions                                                         | 7          |

| <b>2</b>     | Mo    | tivating Example                                                      | 9          |

|              | 2.1   | General structure of affine programs running on a multi-GPU machine . | Ĝ          |

|              | 2.2   | Floyd-Warshall algorithm                                              | 10         |

|              |       | 2.2.1 Per-tile data allocation                                        | 11         |

|              |       | 2.2.2 Inter-GPU coherency                                             | 13         |

|              |       | 2.2.3 Exploiting inter-tile reuse                                     | 13         |

| 3            | Bac   | kground                                                               | <b>1</b> 4 |

|              | 3.1   | Overview of GPU architecture                                          | 14         |

|              |       | 3.1.1 NVIDIA Fermi GPU architecture                                   | 14         |

<u>CONTENTS</u> vi

|   | 3.2 | Open(   | CL programming model                                           | 17 |

|---|-----|---------|----------------------------------------------------------------|----|

|   |     | 3.2.1   | OpenCL terminologies                                           | 17 |

|   |     | 3.2.2   | OpenCL memory hierarchy                                        | 18 |

|   |     | 3.2.3   | OpenCL runtime API                                             | 19 |

|   |     | 3.2.4   | Sample OpenCL code                                             | 20 |

|   | 3.3 | Polyh   | edral model                                                    | 21 |

| 4 | BB  | MM -    | Bounding Box Based Memory Manager                              | 24 |

|   | 4.1 |         | ling boxes and set operations                                  | 24 |

|   | 4.2 | High-l  | level overview of BBMM                                         | 27 |

|   |     | 4.2.1   | Input to BBMM - computation tile                               | 28 |

|   |     | 4.2.2   | Compile time component                                         | 28 |

|   |     | 4.2.3   | Runtime component                                              | 28 |

|   | 4.3 | Data a  | allocation scheme                                              | 30 |

|   |     | 4.3.1   | Initial bounding box extraction at compile time                | 30 |

|   |     | 4.3.2   | Disjoint set of bounding boxes at runtime                      | 31 |

|   |     | 4.3.3   | Example                                                        | 32 |

|   |     | 4.3.4   | Discussion                                                     | 32 |

|   | 4.4 | Buffer  | management                                                     | 34 |

|   |     | 4.4.1   | Design overview                                                | 35 |

|   |     | 4.4.2   | Inter-tile data reuse                                          | 35 |

|   |     | 4.4.3   | Freeing up space on a GPU – box-in and box-out                 | 37 |

|   |     | 4.4.4   | Relationship between tiles, bounding boxes and multiple GPUs . | 38 |

|   | 4.5 | Inter-0 | GPU coherency                                                  | 38 |

|   |     | 4.5.1   | High-level overview of BBMM's coherency scheme                 | 39 |

|   |     | 4.5.2   | Details of BBMM's coherency scheme                             | 39 |

|   | 4.6 | Host a  | and kernel code generation                                     | 41 |

|   |     | 4.6.1   | Structure of the generated host code                           | 42 |

|   |     | 4.6.2   | Structure of the parameterized GPU kernel                      | 43 |

|   | 4.7 | Imple   | mentation                                                      | 44 |

|   | 4.8 | Exper   | imental setup and benchmarks                                   | 45 |

|   | 4.9 | Evalua  | ation parameters and results                                   | 46 |

|   |     | 4.9.1   | Overhead of the runtime library                                | 46 |

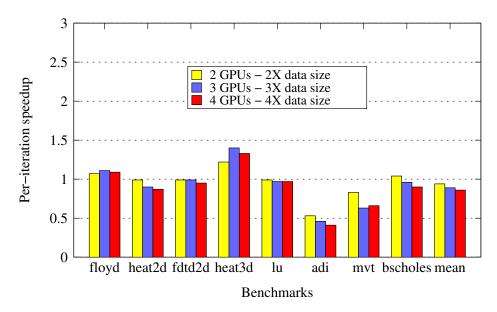

|   |     | 4.9.2   | Performance of programs with data scaling                      | 47 |

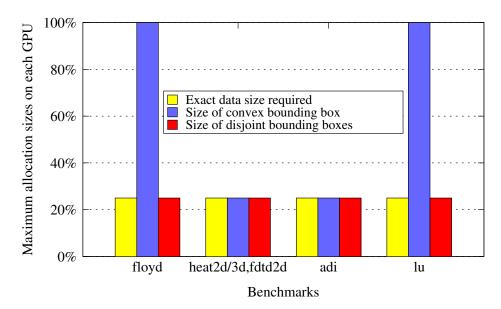

|   |     | 4.9.3   | Comparison of data allocation sizes                            | 48 |

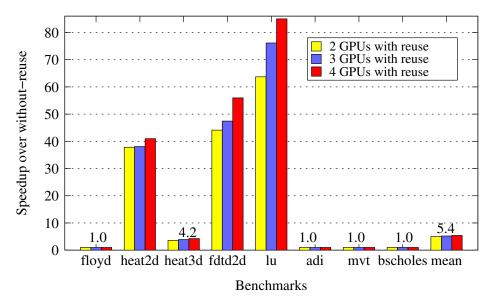

|   |     | 4.9.4   | Benefits of inter-tile data reuse                              | 49 |

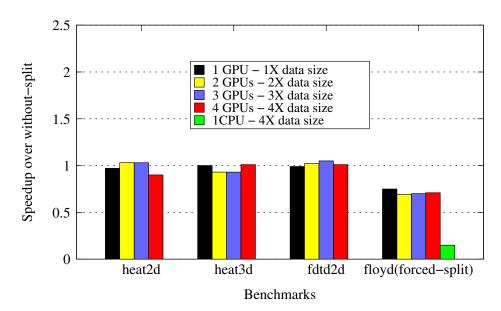

|   |     | 4.9.5   | Effect of access function split                                | 50 |

|   |     | 4.9.6   | Benefit of box-in and box-out                                  | 51 |

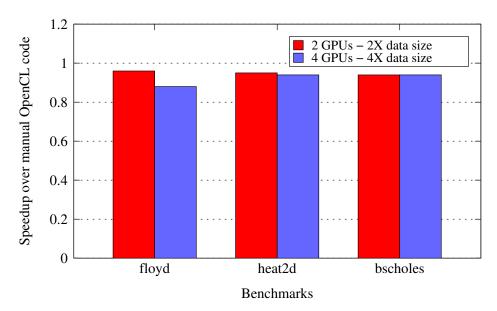

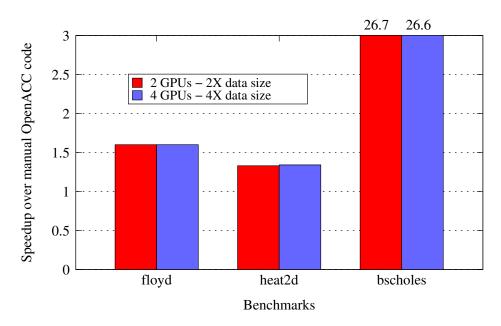

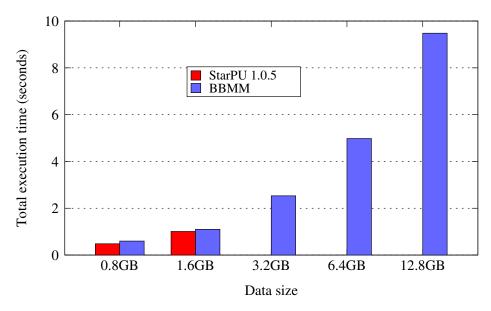

|   |     | 4.9.7   | Comparison with manual code                                    | 52 |

| 5 | Dat |         | ement scheme: Details and further optimizations                | 57 |

|   | 5.1 | Brief o | description of the schemes                                     | 57 |

|   |     | 5.1.1   | The Flow-Out (FO) scheme                                       | 57 |

|   |     | 5.1.2   | The Flow-Out Partitioning (FOP) scheme                         | 58 |

**CONTENTS** vii

|        |             | 5.2.1  | Experimental setup                                | 59 |  |  |

|--------|-------------|--------|---------------------------------------------------|----|--|--|

|        |             | 5.2.2  | Benchmarks                                        | 60 |  |  |

|        |             | 5.2.3  | Evaluation                                        | 60 |  |  |

|        |             | 5.2.4  | Results                                           | 60 |  |  |

| 5.3 Fu |             | Furthe | er optimizations: Maximizing compute-copy overlap | 61 |  |  |

|        |             | 5.3.1  | Compute-copy overlap                              | 63 |  |  |

|        |             | 5.3.2  | Compute-copy overlap in our framework             | 64 |  |  |

|        |             | 5.3.3  | Implementing compute-copy overlap                 | 64 |  |  |

|        |             | 5.3.4  | Maximizing compute-copy overlap                   | 65 |  |  |

|        | 5.4         | Exper  | imental results                                   | 67 |  |  |

| 6      | Rela        | ated V | Vork                                              | 70 |  |  |

| 7      | Conclusions |        |                                                   |    |  |  |

|        | 7.1         | Summ   | nary                                              | 75 |  |  |

|        | 7.2         | Future | e work                                            | 76 |  |  |

| R      | efere       | nces   |                                                   | 77 |  |  |

### List of Tables

| 4.1 | Set operations of BBMM and their overhead              |

|-----|--------------------------------------------------------|

| 4.2 | Functions provided by the buffer manager               |

| 4.3 | Functions provided by the data movement component      |

| 4.4 | Programs used for evaluation                           |

| 5.1 | Results on the Intel-NVIDIA system                     |

|     | Results on the AMD system                              |

|     | Results of compute-copy overlap                        |

| 6.1 | Existing data allocation and buffer management schemes |

## List of Figures

| 1.1  | Multi-GPU machine setup (Photo Courtesy: AMD)                        | 2  |

|------|----------------------------------------------------------------------|----|

| 2.1  | General structure of an affine loop nest for a multi-GPU machine     | 11 |

| 2.2  | Floyd-Warshall code                                                  | 12 |

| 2.3  | Per-tile data allocation, coherency and reuse exploitation           | 12 |

| 3.1  | Fermi Architecture (Courtesy:NVIDIA)                                 | 15 |

| 3.2  | Floyd-Warshall code on cpu                                           | 21 |

| 3.3  | Floyd-Warshall opencl host code                                      | 22 |

| 3.4  | Floyd-Warshall opencl kernel code                                    | 22 |

| 3.5  | Sample affine loop code                                              | 23 |

| 3.6  | Polyhedral representation of a simple loop                           | 23 |

| 4.1  | Data transfer time for various access shapes                         | 27 |

| 4.2  | High-level overview of BBMM                                          | 29 |

| 4.3  | Initial bounding boxes for a tile                                    | 33 |

| 4.4  | Buffer management component of BBMM                                  | 34 |

| 4.5  | General structure of the parameterized GPU kernel                    | 44 |

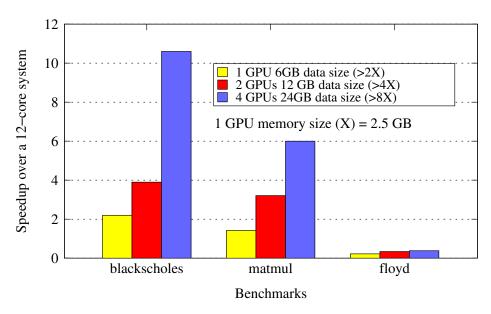

| 4.6  | Performance with data-scaling                                        | 48 |

| 4.7  | Allocation size comparison                                           | 49 |

| 4.8  | Speedup with inter-tile reuse as compared to without-reuse           | 50 |

| 4.9  | Performance with access function splits as compared to without-split | 51 |

| 4.10 | Speedup with box-in and box-out over a 12-core system                | 52 |

| 4.11 | Performance normalized to manually written multi-GPU OpenCL code . | 54 |

|------|--------------------------------------------------------------------|----|

| 4.12 | Performance normalized to manually written multi-GPU OpenACC code  | 55 |

| 4.13 | Comparison with StarPU for mvt on 1 GPU                            | 55 |

|      |                                                                    |    |

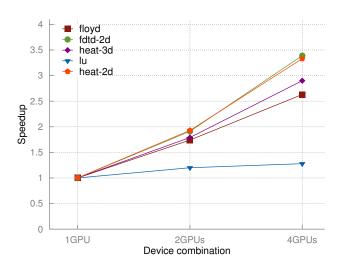

| 5.1  | FOP – strong scaling on the Intel-NVIDIA system                    | 62 |

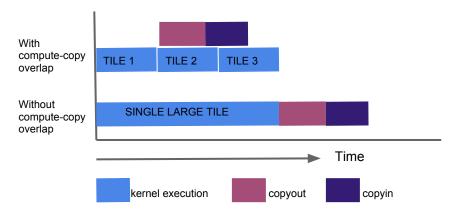

| 5.2  | Benefit of Compute-copy overlap                                    | 65 |

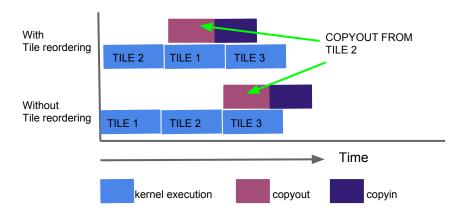

| 5.3  | Compute-copy overlap with and without tile reordering              | 65 |

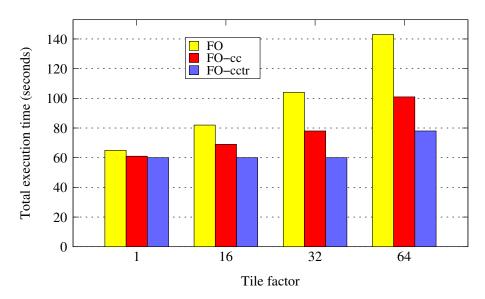

| 5.4  | Performance of tile reordering with varying tile sizes             | 67 |

## List of Algorithms

| 1 | Extracting initial bounding boxes | 31 |

|---|-----------------------------------|----|

| 2 | Computing disjoint bounding boxes | 31 |

| 3 | Initializing a bounding box       | 36 |

| 4 | Structure of generated host code  | 43 |

### Chapter 1

### Introduction

### 1.1 GPUs in high performance computing

In the nineties, the use of GPU was mainly restricted to graphics processing. processor cores and memory inside GPUs were all designed and optimized to be good at pixel shading – so much so that the cores were termed as shaders. All the processing elements executed the same instruction in parallel on an independent pixel element in a Single Instruction Multiple Data (SIMD) manner. Since 2000s, researchers have found ways to utilize the massively parallel power of GPUs for general purpose scientific computations [15] and in the last decade this has gained significant traction. To be suitable for general purpose computations, GPUs have undergone significant evolution in terms of both hardware and the associated software infrastructure. Such GPUs are commonly referred to as General Purpose GPUs (GPGPUs). Today GPGPUs have become a key component in High Performance Computing (HPC) setups. In the June 2013 list of the top 500 supercomputers, 16 of the top 100 supercomputers contain both CPU and GPU processors [40]. This has led to an enormous amount of research and development efforts towards a software ecosystem (mainly compilers and runtime libraries) for GPGPUs, that can achieve better performance, improve their ease of use, and integrate them with the CPU as a seamless heterogeneous system. From now on, we just use the term GPU to refer to GPGPU.

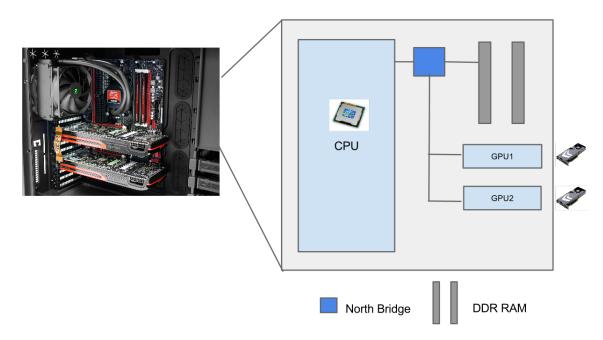

Figure 1.1: Multi-GPU machine setup (Photo Courtesy: AMD)

### 1.2 Towards Multi-GPU machines

Once the benefits of using GPUs became clear, scientists and researchers started using more than one GPU on a single machine to further increase its computing capacity. Today, multi-GPU machines are becoming commonplace in HPC setups. These machines are being used both as standalone workstations to run computations on medium to large data sizes (tens of gigabytes) and as a node in a CPU-MultiGPU cluster handling very large data sizes (hundreds of gigabytes to a few terabytes).

A schematic diagram of a multi-GPU machine is shown in Figure 1.1. It consists of a host CPU and one or more GPUs connected on the PCIex slots. The CPU memory (DDR RAM) is connected through the memory controller (North bridge). The PCIex bus that interconnects the GPUs also connects to the north bridge. However, each of the GPUs have their own memory, and they do not share the address space with either the CPU or with other GPUs. Hence, all the data needed by the computations has to be explicitly copied from the CPU onto each GPU before computations are run and

once the computations complete, the results have to be explicitly copied back. Whenever the computations on a GPU update their own memory, the updations have to be synchronized across all the GPUs through inter-device data transfers in order to satisfy the program dependences.

# 1.3 Programming challenges on a multi-GPU machine

Programming a multi-GPU machine to efficiently utilize its combined power is not straight forward. Programmers have to address multiple non-trivial challenges. In this section we briefly review the important ones.

### 1.3.1 Computation partitioning and load balancing

In order to utilize the combined processing power of all the GPUs, the computations have to be partitioned into tasks and each task has to be scheduled on the available GPUs. The data required for these computations has to be explicitly copied to each GPU. Also, to ensure that the compute resources are optimally utilized, the partitioning has to be load balanced according to the capability of each GPU.

### 1.3.2 Data allocation and buffer management

Once the tasks have been distributed onto the GPUs, the data required by a task have to be allocated on the GPU on which it runs. GPUs have limited memory – typically 3 to 6 GB. Hence, applications working on data sizes larger than this size cannot allocate their entire data on a single GPU. In a multi-GPU machine, even if the combined memory size of the GPUs is larger than the data size, utilizing them to work on data sizes proportional to the combined memory size is currently not an easy task. Also, inorder to maximize the utilization of the available GPU memory the buffers already allocated on the GPU have to be tracked and reused so that there is no redundant allocation and the associated

data transfers.

#### 1.3.3 Inter-GPU data movement

The GPUs within a node are physically connected on the PCIex bus which has a peak unidirectional and bidirectional bandwidth of 8 GB/s and 16 GB/s respectively. Because of this, inter-GPU data movement becomes the bottleneck when the amount of data transferred between devices is significant. Inefficient data movement schemes can result in cost overhead which overcomes the benefit of computation distribution onto multiple GPUs. Hence minimizing the data movement between GPUs is of paramount importance to minimize the overall execution time. Also, for many programs even minimal data movement volume has significant overhead. One can instead try to hide the overhead by overlapping data movement within the computation time. To achieve a high degree of scalability, this overlap has to be maximized such that all the data movement complete while the computations are still going on.

### 1.3.4 Existing approaches

Traditionally these challenges have been tackled using manual and application specific techniques. This generally involves an expert programmer manually partitioning the computation and/or data, after studying the nature of the problem and distributing these partitions to the available compute devices. This effort is tedious, error prone and time consuming. To ease the effort involved in efficient programming of single/multi-GPU setups, current and past research has tried to automatically handle one or more of the sub-challenges. Some works [4, 5, 23, 24, 41] propose automatic code generation techniques that generate GPU code usually in terms of CUDA [11] or OpenCL [27]. Other works [3, 18, 19, 21, 35, 36] propose runtime techniques to handle task placement and scheduling, data allocation and inter-device data movement. Recent proposals like OpenACC [26] and some proprietary compilers [34, 42] target ease of programming through directive based approach similar to OpenMP. They provide a set of computation

and data directives which can be used to annotate the application. The compiler then automatically generates the GPU code and code for the necessary data transfers.

### 1.4 Affine loop nests

Affine loop nests are loop nests that have affine bounds and the array access functions in the computation statements are affine. A significant body of scientific applications that utilize multi-GPU machines contain computations inside affine loop nests. These include stencils, linear-algebra kernels, dynamic programming codes and data-mining applications. The work presented in this thesis is applicable to all of these.

### 1.4.1 Running affine loop nests on multi-GPU machine

To run affine loop nests with large datasets on a multi-GPU machine and achieve scalable performance, one has to perform the following steps efficiently:

- 1. Break up the loop computations into smaller, parallel task units called *tiles* and distribute them across multiple GPUs.

- 2. Allocate the array data required by each tile on the GPU on which the tile executes.

- 3. Perform the computations on each GPU in parallel.

- 4. Once the computations are run, perform the data transfers which are required to maintain coherency between GPUs.

- 5. Aggregate the final results from the GPUs onto the host CPU.

### 1.5 Need for a multi-GPU memory manager

Data allocation, buffer management, and coherency handling is a critical part of the above steps. From this aspect, currently, applications utilizing multiple GPUs resort to manual programming efforts which are often tedious, time consuming and error-prone.

Existing works in this area are either manual, application-specific techniques [3, 11, 26], or automatic schemes [21] that have limitations and inefficiencies in terms of allocation sizes, reuse exploitation, coherency costs and scalability. Hence, an automatic memory management framework for multi-GPU machines that can overcome these shortcomings and enable applications to achieve scalable performance is much needed. In this thesis, we present the design of such an automatic multi-GPU memory manager that embeds itself into steps (2), (4) and (5) above, and performs those tasks efficiently on behalf of the application.

### 1.5.1 Desired capabilities

An important metric in measuring the effectiveness of a multi-GPU memory manager is its ability to allow applications to maximize the utilization of GPU memory. It should enable applications to work with large dataset sizes proportional to the combined GPU memory size without any loss in performance. We will refer to this scaling requirement as data scaling. Data scaling can be seen as a form of weak scaling but has an emphasis on data size (memory utilization) rather than on the workload (computation). This notion of weak scaling is more precise in the context of our work as we will see.

In order to achieve high degree of data scaling, an automatic memory manager should have the following abilities:

- To identify and minimize data allocation sizes for a tile such that the data required by a tile fits within individual GPU memory. Any scheme chosen to achieve this, must also ensure that the cost of accessing the data from a smaller buffer is not significant.

- To identify the data already present on a GPU and reuse it across tiles, thereby minimizing redundant allocations and CPU-GPU data movement costs.

- To keep the data transfers minimal and efficient to reduce overhead.

- To ensure that the overhead of achieving the above tasks do not adversely affect overall execution time of the program.

### 1.6 Bounding Box based Memory Manager

One technique that has been used in certain memory management contexts in the literature is that of bounding boxes [4, 21]. Bounding box of an array, for a given tile, is the smallest hyper-rectangle that encapsulates all the array elements accessed by that tile. Bounding boxes have been mainly used due to the simplicity of accessing the elements in them. In this thesis, we exploit the potential of bounding boxes for memory management far beyond their current usage in the literature, while providing the following key insights:

- Bounding boxes can be subjected to standard set operations like union, intersection, difference etc, at *runtime* merely by performing simple checks and arithmetic on their vertices.

- GPUs are architecturally designed to be efficient at copying rectangular regions of memory.

With the above insights in mind, we propose the Bounding Box based Memory Manager (BBMM). BBMM is a scalable and fully automatic compiler-assisted runtime memory manager for multi-GPU systems. At compile time, it uses static analysis techniques to identify a set of bounding boxes accessed by a computation tile. At runtime, BBMM uses the bounding box set operations to compute a set of disjoint bounding boxes from the set of bounding boxes identified at compile time. This reduces unnecessary and redundant memory allocations. These disjoint bounding boxes are then tracked on a per GPU basis that allows it to maximize inter-tile data reuse and minimize CPU-GPU data movement overhead. All data transfers are performed in terms of bounding boxes thereby exploiting the architectural benefits provided by the GPUs. The runtime operations incur negligible overhead.

### 1.7 Contributions

The main contributions of this thesis are as follows:

- We present the design of a fully automatic, efficient, and highly scalable memory manager for affine loop nests on multi-GPU machines.

- We present a compiler-assisted runtime algorithm to store and manage accessed array data as a set of *disjoint* bounding boxes.

- We present a runtime buffer management scheme that allows applications to (1) maximize inter-tile data reuse thereby maximizing memory utilization and minimizing CPU-GPU data movements, (2) work with data sizes greater than the combined memory size of the GPUs.

- We present an efficient inter-GPU data movement technique that (1) minimizes the volume of data moved due to flow dependences (2) performs all copies efficiently in terms of bounding boxes by exploiting the architectural capability provided by the GPUs (3) maximizes compute-copy overlap and helps to further reduce the data movement overhead.

- Experiments on a system with four GPUs and large dataset sizes showed that, BBMM was able to achieve reduction in data allocation sizes of up to 75% compared to current allocation schemes, achieve at least 88% of the performance of hand-optimized code, and achieve excellent weak scaling.

The rest of this thesis is organized as follows. Chapter 2 gives examples to motivate the important techniques proposed in the thesis. Chapter 3 presents the necessary background material. Chapter 4 is the central chapter of this thesis. It describes the data allocation, buffer management and data movement schemes of BBMM along with the implementation details, experimental results and analysis. Chapter 5 gives more details about the data movement technique used in BBMM and presents the detailed results. It also describes a new technique for maximizing compute-copy overlap and presents the results for the same. Chapter 6 discusses related work and Chapter 7 provides conclusions and future work.

### Chapter 2

### Motivating Example

In this chapter, we present motivating examples that gives the readers a more concrete view of the ideas introduced in the previous chapter. We first provide a brief discussion of the general structure of the code that runs on a multi-GPU machine. We then take Floyd-Warshall algorithm as an example program and illustrate various contributions of this work such as the data allocation scheme, the inter-GPU coherency scheme, and the benefits of inter-tile data reuse. We also motivate the readers to the benefits of our techniques by providing comparative numbers on a sample tile size.

# 2.1 General structure of affine programs running on a multi-GPU machine

An affine program can consist of one or more arbitrarily nested affine loop nests. For an affine loop nest to be suitable to run on a GPU setup, it has to have at least one parallel loop dimension (preferably a parallel band of two or three loops). The parallel loop band can be surrounded by zero or more outer serial loops. Inside the parallel band, there can be more loop dimensions. Each iteration of the parallel band can be executed independently on a GPU thread. The parallel band can be tiled to appropriate size based on the GPU capabilities.

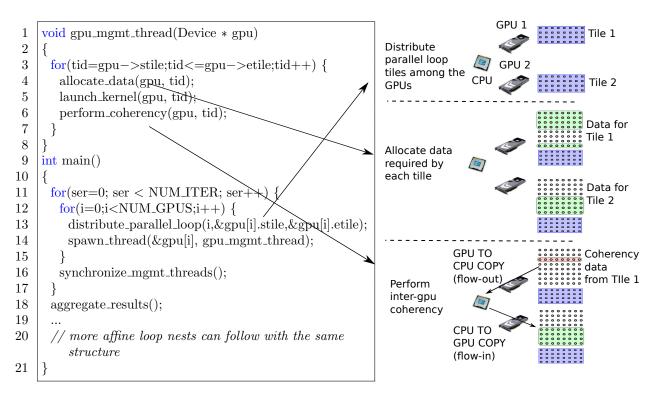

Figure 2.1 illustrates the general structure of a single affine loop nest for a multi-GPU machine. In a program with multiple independent affine loop nests, this structure is repeated for each of them. The execution begins on the host CPU with the outermost serial loop (if it exists) as shown in line 11. For each surrounding serial loop iteration, the tiles of the parallel band are distributed among the available GPUs (line 13). For each tile assigned to a GPU, the data allocation function is called to allocate the necessary data for the tile (line 4). This function is in turn implemented by a memory manager which performs the actual allocations based on its internal schemes. Once the data is ready, the computation kernel is launched. After a tile finishes computation, explicit inter-GPU data movement has to be performed (henceforth referred to as coherency) to ensure that data allocated across GPUs are in sync before the next serial iteration (line 6). This involves two distinct data transfers. The coherency data has to be first copied out of the source GPU that updated the data onto the host CPU. We call it the flow-out transfer (described later in Section 4.5). This data has to be then updated onto the GPUs that need it in the subsequent serial iterations. This is called the *flow-in* transfer. Implementing the coherency scheme efficiently is again the job of the memory manager. At the end of all iterations, the result is aggregated from all GPUs onto the host CPU.

### 2.2 Floyd-Warshall algorithm

The floyd-warshall algorithm computes the shortest-path between every pair of vertices in a directed weighted graph. The input to the algorithm is a path matrix, which is initialized to the cost of edges between a pair of vertices if it exists and infinity otherwise. In each iteration, the algorithm finds the shortest path between any two vertices, passing through a pivot vertex considered in that iteration. This is computed as the minimum value of the current path weight, and the sum of the path weights of the source to pivot and pivot to the destination. Figure 2.2 shows the code for floyd-warshall. It has an outer serial loop k and inner parallel loops i and j. It has a single path array and three distinct access functions, path[i][j], path[i][k],

Figure 2.1: General structure of an affine loop nest for a multi-GPU machine

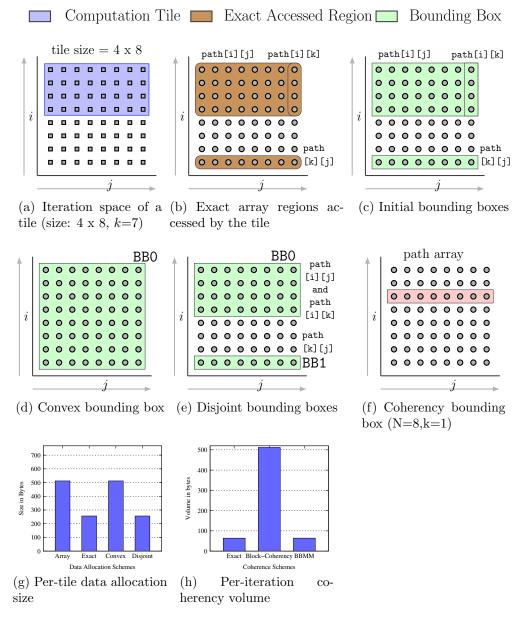

path[k][j]. floyd-warshall has non-uniform array access patterns. Hence, depending on the value of k, these access functions access regions of array that either intersect or are disjoint. Figure 2.3a shows the iteration space for floyd-warshall with N set to 8 and k set to 7. A tile of size 4 x 8 is highlighted. When k is 7, the regions of array accessed by this tile with path[i][j] and path[i][k] overlap, whereas the region accessed with path[k][j] is disjoint from the other two (Figure 2.3b).

#### 2.2.1 Per-tile data allocation

To allocate data for the tile, BBMM first identifies the regions of path array accessed by this tile in terms of bounding boxes (called the *initial bounding boxes*) as shown in Figure 2.3c. Some works in the literature [4, 21] propose to allocate the bounding box over the convex hull of the accessed array regions. Such a scheme would end up allocating the entire array as shown in Figure 2.3d, even though the actual region accessed by the tile is much smaller. BBMM however, performs set operations such as union, intersection,

```

\begin{array}{lll} & \text{for } (k\!=\!0;\ k\!<\!\!N;\ k\!+\!+\!)\ /*\ \text{outer serial loop }*/\\ & \text{for } (i\!=\!0;\ i\!<\!\!N;\ i\!+\!+\!)\ /*\ \text{outer most parallel loop }*/\\ & \text{for } (j\!=\!0;\ j\!<\!\!N;\ j\!+\!+\!)\\ & \text{path}[\,i\,][\,j\,]\!=\!((path[\,i\,][\,k]\!+\!path[\,k\,][\,j\,])\!<\!path[\,i\,][\,j\,])?\,path[\,i\,][\,k\,]\\ & +\!path[\,k\,][\,j\,]\!:\!path[\,i\,][\,j\,]; \end{array}

```

Figure 2.2: Floyd-Warshall code

Figure 2.3: Per-tile data allocation, coherency and reuse exploitation on floyd-warshall

difference etc on these initial bounding boxes and allocates the data required by the tile in terms of disjoint bounding boxes. Figure 2.3e shows the two disjoint bounding boxes for the tile – one for path[i][j] and path[i][k] combined and another disjoint one for path[k][j]. The combined size of the disjoint bounding boxes is much smaller than the bounding box for the convex one as shown in Figure 2.3g and equal to the exact array regions accessed by the tile.

### 2.2.2 Inter-GPU coherency

Dependence analysis of floyd-warshall can show that, in the  $k^{th}$  iteration, a GPU reads the elements of the  $k^{th}$  row, which would have been updated possibly by another GPU, in  $k-1^{th}$  iteration. Hence to maintain coherency, at the end of  $k-1^{th}$  iteration, this row has to be transferred from the source GPU that updated it to all other GPUs. For example, when k is 1, the row highlighted in Figure 2.3f needs to be synced with other GPUs. However, the coherency schemes used in the closely related works [21] transfer the entire data allocation block which contain at least one updated element (henceforth referred to as block-coherency scheme). In our example, this is the bounding box of path[i][j] in the best case (which by itself is much larger than the actual amount of data that need to be synchronized), and almost the entire array in the worst case i.e, when k is 6. Figure 2.3h shows the comparison of data movement volume due to coherency considering only the best case. Even in the best case, there is a difference of  $8 \times$  between the block-coherency scheme and the exact volume required.

### 2.2.3 Exploiting inter-tile reuse

For values of k between 0 and 3, the bounding box required by path[k][j] is already allocated on the GPU as part of the bounding box for path[i][j] (allocated when k was 0). BBMM can very easily detect such data which is already present on the GPU using the subset and superset relationship on bounding boxes. As we show later in the results, many programs perform significantly better with reuse exploitation.

### Chapter 3

### Background

In this chapter, we briefly review the background required for the understanding of the work presented in the thesis. Section 3.1 provides an overview of the GPU architecture. Section 3.2 provides an overview of OpenCL along with a sample program. Section 3.3 provides a brief overview of the Polyhedral framework used in some of the techniques presented in the thesis.

### 3.1 Overview of GPU architecture

In this section, we briefly give an overview of GPU architecture by taking NVIDIA's fermi [13] as the example. Though different GPUs differ slightly in capabilities depending on the workload and cost, the underlying hardware elements do not differ significantly.

#### 3.1.1 NVIDIA Fermi GPU architecture

#### Compute architecture

Fermi consists of a set of 16 streaming multiprocessors (SM), with each SM containing 32 CUDA cores making a total of 512 cores. Each CUDA core consists of a register file with 32,768 32-bit registers, a fully pipelined integer and floating point unit. The floating point unit supports the fused multiply and add (FMA) for both single and double

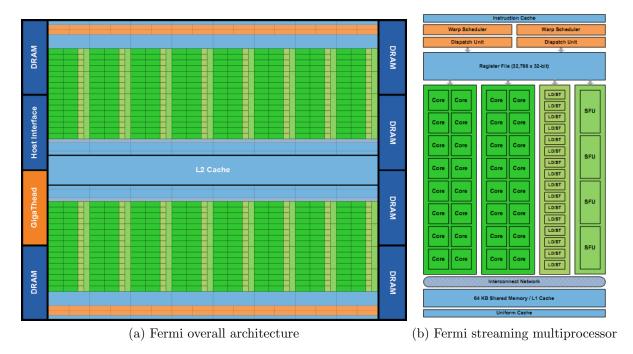

Figure 3.1: Fermi Architecture (Courtesy:NVIDIA)

precision arithmetic. Each SM also consists of 16 load/store units and 4 special function units for executing instructions like sine and cosine. The SM schedules threads in groups of 32 parallel threads called *warps*. Each SM features two warp schedulers and two instruction dispatch units, allowing two warps to be issued and executed concurrently.

#### Memory architecture

Fermi has six 64-bit DRAM memory modules, connected through a 384-bit memory interface. This can support up to 6 GB of global memory that is visible across all SMs. Each SM also has 64 KB of on-chip memory that can be configured either as 48 KB of Shared memory with 16 KB of L1 cache or as 16 KB of Shared memory with 48 KB of L1 cache. It also has a 768 KB of the L2 cache which is shared across all the SMs. GPU memories generally have high bandwidth, but significant latency. Hence, the optimal utilization of memory bandwidth can occur when the accesses to the memory are *coalesced*; i.e, adjacent threads in a warp access adjacent elements in memory.

#### Code execution and data availability

The current GPU architectures including the Fermi, can only work as a co-processor for a host CPU. The GPU itself cannot initiate a program execution. The code that runs on the GPU is referred to as the *kernel*. The host CPU is responsible for scheduling the execution of a kernel on the GPU. Also, GPUs do not share the address space with the host CPU. Hence, the data required by a kernel has to be explicitly copied from the CPU's memory to GPU's memory. Once the kernel completes execution, the responsibility of copying the results from GPU to CPU rests with the CPU.

#### Synchronization and consistency

GPUs provide the following two methods of synchronization.

- Threads within a SM can synchronize using barrier synchronization primitives.

- Threads across SMs can synchronize by implementing synchronization primitives such as mutexes, with the help of atomic operations such as atomic compare and swap, provided by the GPU.

GPUs only guarantee a relaxed consistency model [16]. Threads within a single SM can share data efficiently using the fast barrier synchronization primitives. However, for threads across SMs, the changes made by threads of one SM is only guaranteed to be visible to threads of other SMs only across kernel calls.

#### Communication between host and GPU

The communication between the Host and the GPU involves the following three components: PCIe bus, Command Processor, and DMA transfers.

PCI-express bus Communication and data transfers between the system and the GPU compute device occur on the PCIex channel. Generation 1 x16 has a theoretical maximum throughput of 4 GB/s in each direction. Generation 2 x16 doubles the throughput to 8 GB/s in each direction. Transfers from the system to the GPU compute

device are done either by the command processor or by the DMA engine. The GPU compute device also can read and write system memory directly from the compute unit through kernel instructions over the PCIe bus.

The command processor The host application interacts with the OpenCL devices, through an intermediate driver layer that sends the commands to the hardware on behalf of the application. The commands to the GPU compute device are first buffered in a command queue on the host side. The command queue is then sent to the GPU compute device and processed by it. The commands are executed inorder unless explicitly specified otherwise.

**DMA transfers** Direct Memory Access (DMA) memory transfers can be executed separately from the command queue using the DMA engine on the GPU compute device. DMA calls are executed immediately and the order of DMA calls and command queue flushes is guaranteed. DMA transfers are executed concurrently with other GPU operations. Due to this, DMA transfers can be potentially used as a source of parallelism.

### 3.2 OpenCL programming model

In order to ease the effort involved in programming heterogeneous architectures, an industry consortium [20] consisting of major CPU/GPU vendors proposed OpenCL (Open Compute Language) [27] as a unified programming language. OpenCL - a dialect of C/C++, is a framework for writing programs that execute across heterogeneous platforms consisting of CPUs, GPUs, DSPs and other processors. OpenCL provides a logical architecture and an API, which all compute device vendors supporting OpenCL have to implement. This frees up the programmer from knowing the details of each vendor architecture and focus on the application logic.

### 3.2.1 OpenCL terminologies

Work-item The smallest unit of work on an OpenCL device.

Work-group A collection of work-items, all of which are mapped to the same SM.

**Wavefront** A collection of work-items which execute simultaneously in a single lock-step. A wavefront is also known as a warp.

**NDRange** The arrangement of work-groups and work-items into a n-dimensional grid.

**Kernel** The C code that contains the computation logic and executed by a work-item.

**Context** The environment within which work-items execute. This includes devices and their memories and command queues.

Compute device The OpenCL device that executes the kernel.

**Command queue** A structure into which all the commands sent to a compute device are queued.

### 3.2.2 OpenCL memory hierarchy

OpenCL has four memory domains: private, local, global, and constant.

**Private memory** specific to a work-item and not visible to other work-items.

**Local memory** specific to a work-group and accessible only by work-items belonging to that work-group.

Global memory accessible to all work-items executing in a context, as well as to the host (read, write, and map commands).

**Constant memory** read-only region for host-allocated and initialized objects that are not changed during kernel execution.

**Host (CPU) Memory** host-accessible region for an application's data structures and program data.

An OpenCL program consists of a host part and a kernel part. The host code is run on a CPU which hosts the compute devices and performs the tasks of managing the compute devices, scheduling computations on them, transferring data to/from them, and aggregating the final computed result. The host CPU can also act as a compute device. The kernel code contains the actual computations and are run on the compute devices. The compute devices are exposed to the programmer in terms of logical threads, which are in turn grouped into thread-blocks. The computations are mapped onto these threads and thread-blocks such that each thread performs computations on a small portion of data in parallel with other threads in a SIMD manner. Each compute device have their own memory space. The data required by the computations have to be explicitly allocated on each compute device and doing this is the responsibility of the host CPU. Once computations are performed, the results have to be explicitly copied from compute device memory onto the host CPU memory. For a more detailed specification of the OpenCL standard and the API, the reader is referred to the Khronos website [27].

### 3.2.3 OpenCL runtime API

Device, Context, and Command queue The context is the primary management structure of OpenCL. A context encapsulates one or more devices, along with their command queues and the kernel to be run. A context can be created using clCreateContext(). The OpenCL devices of a particular type (CPU, GPU etc) can be discovered using the clGetDeviceIDs() function. A command queue can be created under a context using the clCreateCommandQueue(). Command queues can either be configured to process the messages inorder or out-of-order.

Kernel creation and launch OpenCL program may be created from source using clCreateProgramWithSource() or loaded as binaries using clCreateProgramWithBinary(). In either case this must be followed by clBuildProgram(). The OpenCL compiler may

be a dynamically linked library. A kernel can be created using clCreateKernel() function. Arguments can be passed to the kernel using clSetKernelArg().

Memory management Global memory is allocated using clCreateBuffer(). Memory can be created with MEM\_READ\_ONLY, MEM\_WRITE\_ONLY, MEM\_READ\_WRITE flags. Memory is freed using clReleaseMemObject(). Variables can be allocated on the on-chip local memory by annotating the variables with the \_\_local\_\_ qualifier.

Data transfers Data can be transferred from the CPU to the GPU and vice-versa using the clEnqueueReadBuffer() and clEnqueueWriteBuffer(). Another technique is to map the GPU's device buffer into CPU's address space using the clEnqueueMapBuffer() and once the memory is mapped, data can be read and written from the GPU using the regular memcpy() function. However, mapping the GPU buffer performs a copy of the data from the GPU into the CPU buffer. This is an expensive operation and should be avoided unless absolutely required. OpenCL also provides functions to transfer a non-contiguous rectangular region of memory using clEnqueueReadBufferRect() and clEnqueueWriteBufferRect() functions. This is a crucial capability we use in our work.

### 3.2.4 Sample OpenCL code

Figure 3.2 shows the floyd-warshall code as it is typically written in C for the CPU. The memory for the path array can be can be allocated either on the data segment through global declaration, or on the heap through dynamic allocation. The program consists of three loops - k, x and y. A quick dependence analysis can show that the k loop is serial while the y and x loop can be run in parallel.

Figure 3.3 and Figure 3.4 show the the OpenCL equivalent code for the same. The code consists of a host part and the kernel part. The execution of the program begins with the host code obtaining the OpenCL platform id and the device list. Then it goes on to create a context and a command queue for the chosen compute devices. The memory for the path array is explicitly allocated on the GPU's global memory. This is followed

```

void Floyd()

1

2

3

int x, k, y;

4

for(k=0; k < NUM_NODES; k++)</pre>

5

6

7

for(y=0; y < NUM_NODES; y++)</pre>

8

for(x=0; x < NUM_NODES; x++)</pre>

9

10

path[y][x] = ((path[y][k] + path[k][x]) < path[y][x]) ? (path[y][k] + path[k]

11

][x]):path[y][x];

12

13

14

15

}

```

Figure 3.2: floyd-warshall code on cpu

by choosing of the right sizes for the NDRange.

Among the three loops of floyd-warshall, the k loop is run on the CPU sequentially, and for each iteration of this loop, the y and x loops are executed on the GPU in a DOALL parallel manner. Figure 3.4 shows the structure of the OpenCL kernel. As we can see, each array index is mapped to a thread in the OpenCL n-dimensional (2D in this case) grid. Each thread now executes one instance of the statement corresponding to its index in each dimension. At the end of execution of all serial iterations the result is copied explicitly from the GPU onto the CPU result buffer.

### 3.3 Polyhedral model

The polyhedral model provides a framework to compactly capture the execution sequence of statements present inside arbitrarily nested affine loops. The model provides a way to represent, analyze, and transform iterations of affine loop nests by treating them as integer points inside a convex polyhedron. For a statement inside an affine loop nest, the surrounding loop iterators along with program parameters form the dimensions of the polyhedron that represents the statement's execution domain. The upper and lower bounds of each loop iterator are represented as linear inequalities. These inequalities form

```

1

void launch_opencl_kernel()

2

3

clGetPlatformInfo(platform_id,CL_PLATFORM_VERSION,sizeof(str_temp),str_temp,NULL);

clGetDeviceIDs(platform_id, CL_DEVICE_TYPE_GPU, 2, &device_id[0], &num_devices);

4

5

clGetDeviceInfo(device_id[1],CL_DEVICE_NAME, sizeof(str_temp), str_temp,NULL);

6

7

clGPUContext = clCreateContext( NULL, 1, &device_id[1], NULL, NULL, &errcode);

8

9

clCommandQueue = clCreateCommandQueue(clGPUContext, device_id[1], 0, &errcode);

10

11

path_mem_obj = clCreateBuffer(clGPUContext, CL_MEM_READ_WRITE, NUM_NODES *

NUM_NODES * sizeof(DATA_TYPE), NULL, &errcode);

12

13

localWorkSize[0] = 16; localWorkSize[1] = 16;

globalWorkSize[0] = NUM_NODES; globalWorkSize[1] = NUM_NODES;

14

15

16

for(t1 = 0; t1 < NUM_NODES; t1 ++)</pre>

17

errcode = clSetKernelArg(clKernel, 0, sizeof(cl_mem), (void *)&path_mem_obj);

18

errcode = clSetKernelArg(clKernel, 1, sizeof(cl_int), &t1);

19

20

errcode |= clSetKernelArg(clKernel, 2, sizeof(cl_int), &NUM_NODES);

21

22

errcode = clEnqueueNDRangeKernel(clCommandQueue, clKernel, 2, NULL,

globalWorkSize, localWorkSize, 0, NULL, NULL);

23

24

clFinish(clCommandQue);

25

}

26

27

errcode = clEnqueueReadBuffer(clCommandQue, path_mem_obj, CL_TRUE, 0, NUM_NODES*

NUM_NODES*sizeof(DATA_TYPE), &path_outputFromGpu[0][0], 0, NULL, NULL);

28

```

Figure 3.3: floyd-warshall opencl host code

```

\_kernel 	ext{void} computeKernel(\_global DATA\_TYPE * pdm, uint numNodes, uint my\_rank,

1

int my_start, int my_end, int t1)

2

3

int xValue = get_global_id(0);

4

int yValue = get_global_id(1);

5

6

int k = t1;

7

8

DATA_TYPE oldWeight = pdm[yValue * numNodes + xValue];

9

DATA_TYPE tempWeight = (pdm[yValue * numNodes + k] + pdm[k * numNodes + xValue]);

10

11

if (tempWeight < oldWeight) {</pre>

12

pdm[yValue * numNodes + xValue] = tempWeight;

13

}

14

}

```

Figure 3.4: floyd-warshall opencl kernel code

```

for (i=0; i<N; i++)

for (j=0; j<N; j++)

A[i][j]= A[i+1][j]+A[i-1][j]; /* computation statement */</pre>

```

Figure 3.5: Sample affine loop code

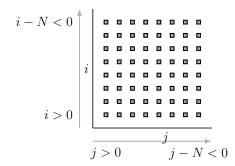

Figure 3.6: Polyhedral representation of a simple loop

the faces of the polyhedron. The set of all integer points inside a polyhedron formed by the bounds of the loop iterators surrounding a statement is called the *iteration space* of the statement. Each point in an iteration space is called an *iteration vector*, and is represented by a *n*-tuple, where *n* is the dimensionality of the iteration space. In an affine loop nest, all array accesses in the computation statements have to be affine functions of the outer loop iterators and program parameters. Such an affine function which is used as a subscript to access the elements of an array is called as an *access function*. The set of all array elements accessed by an individual access function is called the *data space* of the access function. The polyhedral framework provides libraries to perform various operations such as union, intersection, difference on these polyhedra [17, 33]. For more details on the polyhedral framework, the readers are referred to [6].

Figure 3.5 shows a two dimensional affine loop nest with a single computation statement. As we can see, the loop bounds and the array subscripts are all affine functions of the loop variables i and j. N is the program parameter whose value at runtime determines the exact number of points in the iteration space. Figure 3.6 shows the polyhedral representation of the iteration space of this statement. For ease of depiction, we have chosen N to be 8. The linear inequalities that form the bounds of the iteration space are also shown. Array subscripts i, i + 1, i - 1, and j are the access functions.

# Chapter 4

# BBMM - Bounding Box Based Memory Manager

This chapter forms the core part of this thesis – the Bounding Box based Memory Manager. Section 4.1 begins with the definition of a bounding box, the key idea of performing set operations on bounding boxes, the advantages using bounding boxes for GPU memory management. Section 4.2 gives an overview of each component of BBMM with an illustrative diagram. Section 4.3 describes the data allocation algorithms. Section 4.4 describes the buffer management scheme. Section 4.5 gives the details of the inter-GPU coherency scheme used in BBMM. Section 4.6 gives the overall structure of the generated code and this is followed by sections containing experimental evaluation, results and their detailed analysis.

# 4.1 Bounding boxes and set operations

In this section, we give the definition of bounding boxes, describe the core insights about performing set operations on them. We then justify the the advantages of using bounding boxes for GPU memory management.

Bounding box: BBMM allocates and manages data in terms hyper-rectangles. A hyper-rectangle is an n-dimensional counterpart of a rectangle, i.e., it has two parallel

faces for each dimension that bound the rectangle along that dimension. The smallest hyper-rectangle encapsulating a point set is called the *bounding box* of that set. In our context, a bounding box is the smallest hyper-rectangle encapsulating the elements of a multi-dimensional array which are read or written through an access function in a computation statement of a program.

| Function Name     | Description                                                                                     | Overhead                                             | Illustration                                                         |

|-------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------|

| bb_convex_union() | Gives the convex<br>hull of the array el-<br>ements in the two<br>bounding boxes                | two bound checks in<br>each dimension                | bb_convex_union(BB1,BB2) = BB3 BB1 BB3 BB2 BB2                       |

| bb_simple_union() | Performs the union of the array elements in the two bounding boxes                              | simple append, dimension independent                 | bb_simple_union(BB1,BB2) = BB1 + BB2 BB1 BB2 BB2 BB2                 |

| bb_intersection() | Performs an intersection of two bounding boxes                                                  | at most eight bound<br>checks in each dimen-<br>sion | bb_intersection(BB1,BB2) = BB3 BB1 BB3 BB2                           |

| bb_subtract()     | Subtracts one<br>bounding box from<br>another, returning<br>a simple union of<br>bounding boxes | four assignments (two cuts) in each dimension        | bb_subtract(BB1,BB2) = BB3 BB1 BB3 BB2                               |

| bb_is_subset()    | Checks if one<br>bounding box is a<br>subset of another                                         | two bound checks in each dimension                   | bb_is_subset bb_is_subset (BB1,BB2)=No (BB1,BB2)=Yes BB1 BB1 BB2 BB2 |

Table 4.1: Set operations of BBMM and their overhead

Set operation on bounding boxes: The integer points inside the bounding boxes can be subjected to common set operations like union, intersection, difference, finding subset and superset relations. Table 4.1 lists and illustrates these operations. Using them, BBMM can perform various memory optimizations such as refining compiler generated

bounding boxes, exploiting inter-tile reuse, minimizing data movement overhead etc. Note that subtraction can create multiple bounding boxes. In such cases, a simple union of these is returned. All functions of BBMM work on a simple union of bounding boxes.

The following are the advantages of using bounding boxes for GPU memory management.

- 1. Negligible runtime overhead: One key advantage of working with bounding boxes is that the set operations can be done at runtime merely by performing simple checks and arithmetic on their vertices. For an n-dimensional bounding box, one needs to operate on  $2^n$  vertices. As we deal with values of n that are small enough (even for a rare case of a 5D array one needs to perform simple operations on just 32 vertices), these operations have negligible runtime overheads. This allows it to scale easily to manage a large number of GPUs.

- 2. Simplicity and low cost of access functions: An array element present in a bounding box can be accessed by simply subtracting the lower bound offsets of the bounding box from the array index in each dimension. For example, for any array a, an element a[i][j] present in a bounding box  $\{lb_i, ub_i, lb_j, ub_j\}$  can be accessed by subtracting the lower bounds from each dimension, i.e., as  $a[i-lb_i][j-lb_j]$ , where  $lb_i$  and  $lb_j$  are lower bounds of the bounding box along dimension i and j respectively.

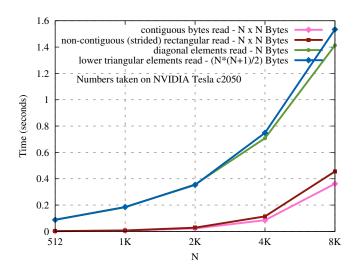

- 3. Architectural support for rectangular transfers on GPUs: GPUs (especially the ones used in high performance computing) are architecturally designed to be efficient at copying rectangular regions of memory to and from the CPU. The GPU programming models such as OpenCL and CUDA expose this capability to the user by providing rectangular copy APIs; for example, OpenCL provides clenqueueReadBufferRect() and clenqueueWriteBufferRect(). Using these APIs, we find that non-contiguous (strided) rectangular transfers of data between CPU and GPU, are almost as efficient as transferring contiguous bytes (Figure 4.1). This may be due to internal packing of non-contiguous elements before performing a single DMA to transfer

Figure 4.1: Data transfer time for various access shapes

it to destination buffers on the CPU. The same is done by the runtime driver during CPU to GPU transfers. These non-contiguous rectangular transfers are more efficient than performing multiple individual reads to transfer arbitrary nonrectangular shaped regions (say a diagonal or a triangle) of much smaller size.

4. Non-scalability of precise data allocation techniques: Größlinger [14] proposed a precise data allocation technique in the context of scratchpad memory management. However, the cost of access functions computed through this technique can become prohibitively high (elaborated in Chapter 6), thus making it impractical.

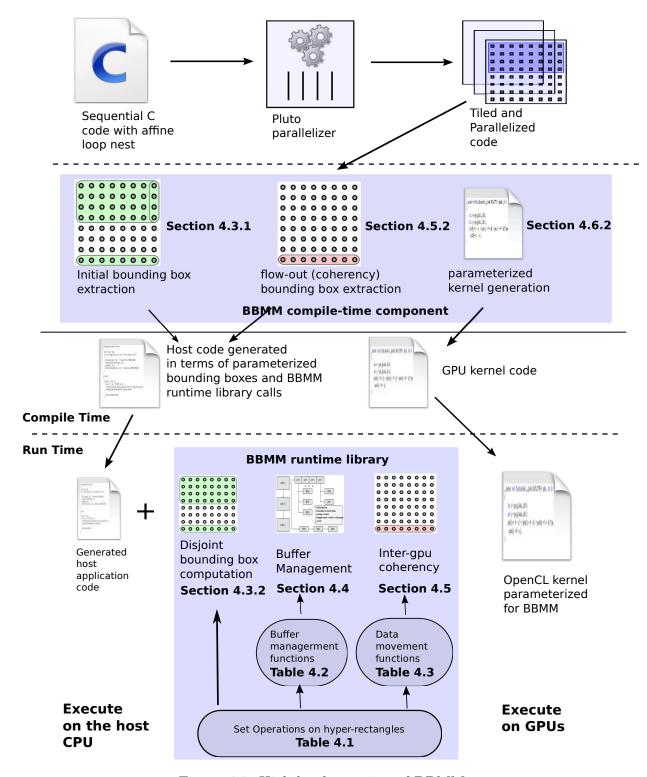

# 4.2 High-level overview of BBMM

In this section, we give a high-level view of the various components of BBMM. Figure 4.2 shows the inter-working of the input, the compile-time and the runtime components. The figure has three distinct sections separated by two dashed lines. The first section shows the input to BBMM. The second section depicts BBMM's compile time component. The third section depicts BBMM's runtime component. The arrows indicate the order of execution of each component and sub-component. Each section produces a specific output which is used as input in the next section. Below we provide additional details

for each component.

# 4.2.1 Input to BBMM - computation tile

BBMM expects the loop nests to be parallelized and tiled to suit GPU architectures. Hence, the input sequential C code with affine loop nests is first passed through the Pluto [31] auto-parallelizer. Pluto automatically identifies any parallelism present in the loop nests and generates a tiled and parallelized version of the loop code. In our framework, a parallelized loop nest has zero or more outer serial loops surrounding the parallel loops. The serial loops are run on the host CPU which schedules the parallel loops to run on the GPUs. The outermost parallel loop is broken down into pieces of suitable sizes (tiles) and these tiles are distributed onto available GPUs. A tile therefore is an iteration vector representing one iteration of the distributed parallel loop. All algorithms in BBMM work at the granularity of a tile.

# 4.2.2 Compile time component

At compile time, BBMM takes a tile as input and extracts the parameterized bounding boxes which are later refined and used at runtime. These bounding boxes are parameterized on the input tile and array. The compile-time generates the application code that refine these bounding boxes at runtime and performs various buffer management tasks. The code is generated in terms of calls to the BBMM's runtime library. The compile-time also generates the GPU kernel that accepts bounding boxes as parameters.

# 4.2.3 Runtime component

The runtime component of BBMM is the runtime library that is linked with the code generated at compile time. The library consists of key functions of BBMM. This includes

• Hyper-rectangular set operations used to refine the bounding boxes and thereby minimize memory allocation

Figure 4.2: High-level overview of BBMM

- Buffer management functions that track bounding boxes on a per GPU basis and performs various memory optimizations

- Inter-gpu data movement functions that maintain coherency of data between GPUs

This runtime library is linked with the application code generated by the compile-time stage and executed on the host CPU. The parameterized kernel is executed on the GPU devices.

# 4.3 Data allocation scheme

In this section, we describe the data allocation scheme used in BBMM. The data allocation scheme is responsible for *identifying* the regions of array accessed by a tile and *minimizing* the memory allocated for it on the GPU. We propose a compiler-assisted runtime data allocation scheme. At compile time, an initial set of bounding boxes - one for each access function of the input tile is extracted. At runtime, these bounding boxes are further refined into a set of disjoint bounding boxes.

# 4.3.1 Initial bounding box extraction at compile time

This is done using a simple polyhedral technique as shown in Algorithm 1. For each read or write access function of the array, the algorithm invokes the following functions:

get\_data\_polyhedron(): Computes the data space by taking the image of the iteration space over the access function.

get\_bounding\_box(): Computes the smallest hyper-rectangle encapsulating all the points in the data space.

The set of bounding boxes returned are parameterized on the input tile and the array. The initial bounding boxes extracted at this stage could completely or partially overlap with one another. Hence, in order to avoid duplicate allocations, we need to refine these initial bounding boxes into a set of disjoint bounding boxes. We note that this refinement operation can be performed at compile time using the polyhedral library. However doing

so at compile time might result in over-allocations since the library has to allocate for the maximum value of the bounds to ensure correctness. Also, the library might choose to perform a large number of splits depending on the type of initial bounding boxes. At runtime, we have the precise bounds for the initial bounding boxes and as mentioned before, the rectangular set operations can be performed with negligible overhead. Hence, we choose to perform the bounding box refinement at runtime.

#### Algorithm 1: extract\_initial\_bounding\_boxes()

```

Input: Computation tile \vec{t}, Array a

1 S_a^{init} = \phi

2 for each read or write access function f_a^i do

3 dp_a^i = \text{get\_data\_polyhedron}(f_a^i)

4 bb_a^i = \text{get\_bounding\_box}(dp_a^i)

5 ddb_a^i to ddb_a^i to

```

#### Algorithm 2: get\_disjoint\_bounding\_boxes()

```

Input: S_a^{init} - Set of initial bounding boxes for tile \vec{t} and array a S_a^{disjoint} = \phi

2 for each bounding box bb_a^{init} in S_a^{init} do

3 bb_a^{rem} = bb_a^{init}

4 for each bounding box bb_a^{disj} in S_a^{disjoint} do

5 bb_a^{intersect} = bb_a^{intersection}(bb_a^{rem}, bb_a^{disj})

6 bb_a^{rem} = bb_a^{intersect}(bb_a^{rem}, bb_a^{intersect})

7 add\ bb_a^{rem} to S_a^{disjoint}

8 Output: S_a^{disjoint}, the set of disjoint bounding boxes for array a

```

# 4.3.2 Disjoint set of bounding boxes at runtime

The key steps of the data allocation scheme are performed at runtime as shown in Algorithm 2. The input is the set of initial bounding boxes now substituted with the actual values for tile and array parameters (since we have this information at runtime). On each of these exact bounding boxes, the algorithm uses the set operations described in Table 4.1 to subtract out the portions which are already present in the set of disjoint

bounding boxes. This is done as shown in lines 2 to 6. The portion that still remains is added to the disjoint bounding box set.

#### 4.3.3 Example

Figure 2.3 illustrates the data allocation scheme for floyd-warshall. Figure 2.3a shows the iteration space of a single tile. For illustration purpose, we have chosen N=8 and k=7. Figure 2.3c shows the initial bounding boxes; one for each distinct access function. path[i][j] covers an area equal to the size of the tile. path[i][k] covers  $N-1^{th}$  column. path[k][j] covers the  $N-1^{th}$  row. Figure 4.3 shows the initial bounding boxes as it looks in the generated code. The generated bounding boxes are parameterized on the input tile represented by the iteration vector (t0, t1, t2, t3) and the input array. The set of initial bounding boxes is input into Algorithm 2. Figure 2.3e shows the result of running Algorithm 2 on initial bounding box list. For the chosen tile, the bounding box of path[i][k] is a subset of the bounding box of path[i][j] whereas bounding box of path[k][j] is disjoint from both. Hence the algorithm returns two disjoint bounding boxes BB0 and BB1 as shown.

#### 4.3.4 Discussion

Access function split and warp divergence: In some cases a single access function of an array can get split among multiple bounding boxes due to the disjoint operation. In these cases, a runtime check has to be made in the computation kernel on the GPU to determine the bounding box which contains a particular array index. If different threads of a warp have to access different bounding boxes, it will result in warp divergence causing loss of parallelism. Though this seems like a problem in theory, in practice this is not an issue due to the following reasons:

• For programs with uniform dependences like stencil computations, the adjacent threads (forming the warp) access adjacent memory locations. Hence, they almost always access data from the same bounding box, i.e., they take the same control

```

list extract_initial_bounding_boxes_for_path_in_kernel_0(Device dev, int t0, int t1,

int t2, int t3, void * array)

2

{

3

// the iteration vector (t0,t1,t2,t3) represents the tile. t1 corresponds to the

4

// serial iteration k. t3 represents the tiled parallel dimension.

5

6

// path[i][j]

7

struct bounding_box * bb0 = bb_alloc(2);

8

bb0->array = array;

9

bb0->flags = BBMM_FLAGS_READ_WRITE;

10

bb0->bp[0].lb = (TILE\_SIZE * t3) + (0);

bb0->bp[0].ub = (TILE_SIZE * t3) + ((TILE_SIZE-1));

11

12

bb0->bp[1].lb = 0;

13

bb0->bp[1].ub = +1*N-1;

14

add_to_list(&init_bb_list, bb0);

15

// path[i][k]

16

struct bounding_box * bb1 = bb_alloc(2);

bb1->flags = BBMM_FLAGS_READ;

17

18

bb1->array = array;

19

bb1->bp[0].lb = (TILE\_SIZE * t3) + (0);

20

bb1->bp[0].ub = (TILE_SIZE * t3) + ((TILE_SIZE-1));

21

bb1->bp[1].lb = (1 * t1) + (0);

22

bb1->bp[1].ub = (1 * t1) + (0);

23

add_to_list(&init_bb_list, bb1);

24

// path[k][j]

25

struct bounding_box * bb2 = bb_alloc(2);

26

bb2->array = array;

27

bb2->flags = BBMM_FLAGS_READ | BBMM_FLAGS_CLEANUP;

28

bb2->bp[0].lb = (1 * t1) + (0);

29

bb2->bp[0].ub = (1 * t1) + (0);

bb2->bp[1].lb = 0;

30

31

bb2->bp[1].ub = +1*N-1;

32

add_to_list(&init_bb_list, bb2);

33

34

return init_bb_list;

35

}

```

Figure 4.3: Compiler generated function that returns initial bounding boxes for a tile

Figure 4.4: Buffer management component of BBMM

flow path, resulting in no performance loss.

• In order to incur a performance loss due to warp divergence, an access function should both be non-uniform (so that adjacent threads forming a warp access different memory regions) and split among multiple bounding boxes. For this loss to be significant, a large number of access functions should have been split among multiple bounding boxes. This happens very rarely in practice. Even when it does happen, the performance loss will not be prohibitively significant.

In Section 4.9, we provide results that support the above reasoning.

# 4.4 Buffer management

In this section, we describe the techniques used in the buffer management component of BBMM. This component is responsible for tracking the bounding boxes allocated on each GPU, reduce duplicate allocations, maximize inter-tile data reuse and provide capability to work with data sizes larger than the available GPU memory.

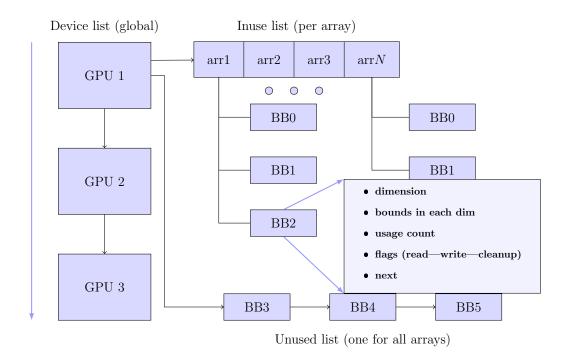

#### 4.4.1 Design overview

Figure 4.4 shows the design of the buffer management component. For each GPU, the buffer manager maintains two lists of bounding boxes: (1) inuse list (2) and unused list. The ones that are currently being read or written by a tile will be in inuse list. The unused list is used to free up memory on a GPU whenever required and is maintained in the least recently used (LRU) order. Each bounding box is associated with a usage count, indicating the number of compute tiles currently using it. A bounding box will be in unused list only if its usage count is zero. The usage count will be important in a setting where multiple parallel tiles are running simultaneously on the same GPU and these tiles are sharing the same bounding box. In such cases, the bounding box should not be freed (say, to make space) until all the tiles are done using the bounding box. It also has flags to indicate whether it will be only read, written, and what all needs to be cleaned up. The memory manager provides various inexpensive runtime functions on the bounding boxes. Table 4.2 lists the important ones.

| Function name | Description                                                                   |

|---------------|-------------------------------------------------------------------------------|

| bb_alloc()    | Allocates a bounding box on a device, making space if needed                  |

| bb_present()  | Checks if a given bounding box is already present on a device                 |

| bb_readin()   | Initializes data into a bounding box, with intra-device transfers if possible |

| bb_cleanup()  | De-allocate bounding boxes that are no longer required                        |

Table 4.2: Functions provided by the buffer manager

#### 4.4.2 Inter-tile data reuse

Using hyper-rectangles allows BBMM to find the subset and superset relation between bounding boxes at runtime, with negligible overhead. It uses this functionality, to reuse the data already present on a device and thereby minimize data transfers from CPU to GPU. Data reuse happens at two levels. In the first level, BBMM checks if a bounding box is already present or fully subsumed on the GPU before it allocates a new bounding box. This check is performed by the bb\_present() function. This avoids redundant allocations.

#### Algorithm 3: bb\_readin()

```

Input: Device dev, Array a, Bounding box bb_a^{new}

1 for each bounding box bb_a^{dev} on the device do

2 bb_a^{intersect} = bb intersection(bb_a^{new}, bb_a^{dev})

3 if bb_a^{intersect} is not empty then

4 | /* part of the data required for this bounding box is already present on the device */

5 | intra_device_copy(bb_a^{new}, bb_a^{dev}, bb_a^{intersect})

6 | bb_a^{new} = bb_subtract(bb_a^{new}, bb_a^{intersect})

6 | /* some portion of the bounding box is not yet read in. copy this data from cpu cpu_copy(bb_a^{new})

```

The second level of reuse happens for partially subsumed bounding boxes. When a new bounding box is allocated on a device, it has to be initialized with the latest data. Instead of doing this entirely with the data from the CPU, BBMM reuses data that is already present on a device through intra-device copies from one bounding box to another. bb\_readin() (Algorithm 3) is used to perform this. The function uses the bb\_intersection() to find the intersection of the new bounding box with the bounding boxes already present on the GPU. The intersecting area is copied to the new bounding box through an intra-device copy and the intersecting area is subtracted out from it. Major GPU programming frameworks such as OpenCL and CUDA provide functions to perform intra-device copies. For example, OpenCL provides clEnqueueCopyBuffer() function that can perform this copy. The process is repeated for all bounding boxes already present on the device. The leftover portion is initialized with the data from the CPU.