# Automatic Storage Optimization of Arrays in Affine Loop Nests

#### A THESIS

SUBMITTED FOR THE DEGREE OF

Doctor of Philosophy

IN COMPUTER SCIENCE AND ENGINEERING

by

Somashekaracharya G. Bhaskaracharya

Computer Science and Automation

Indian Institute of Science

BANGALORE – 560 012

July 2016

© Somashekaracharya G. Bhaskaracharya

July 2016

All rights reserved

My family, friends and colleagues

# **ACKNOWLEDGEMENTS**

I am deeply indebted to my advisor, Dr. Uday Bondhugula, for guiding me at every stage of my research work. It has truly been an honour to work with him. I hope I have justified the trust he invested in me when he agreed to be my advisor, despite the commitment to academic work only being of a part-time nature from my side. His constant support and optimism were major factors in helping me juggle both, academic research and office work at National Instruments, through the various ups and downs in these last five years. He was ever ready to discuss new ideas, however wild (I still remember a discussion on the storage optimization problem we had in the Dubai airport terminal, very late into the night, while waiting for our return flight to Bangalore). And almost invariably, I returned from such discussions with more ideas to work on. This work would, quite simply, not have been possible without his tremendous guidance. I offer my sincerest thanks!

I would like to express my gratitude to Dr. Albert Cohen for all his insightful comments and suggestions. Interactions with him, over email as well as in person every now and then, helped me immensely in refining the ideas presented here. His belief in their merit kept me inspired and motivated. I would also like to thank my organizational supervisor, Dr. Dinesh Nair, who gave me complete freedom in my research work.

I have greatly benefited through help from various other quarters. Firstly, I would like to thank my labmates Chandan, Roshan, Irshad, Vinay, Raviteja, Aravind, Thejas, Vinayak for their generous assistance and suggestions on so many occasions, despite already being burdened with their own work. I am also very grateful to my friends and colleagues at NI who went out of their way in helping me pursue my academic goals to the fullest extent possible – to Anand, Gowrishankar, Rajanikanth for creating this opportunity for me; to Praveen, Subbaiah and Prashanth for their managerial support; and last but not the least, to my team-mates Nikhil, Bharath, Rakesh, Chethan and Ashwin. I would like to acknowledge the monetary assistance provided by NI towards my studies.

As the proverbial dwarf standing on the shoulders of giants, I owe a great deal to the authors of various tools (such as Clan, GLPK, ISL, Pet, Pluto etc) that I have used to implement the ideas presented in this work. Valuable feedback from several anonymous reviewers was also very helpful – my thanks to all these reviewers.

Finally, I would like to dedicate this work to my parents, G. S. Bhaskaracharya and H. K. Pushpa Latha, who have always encouraged me in all my pursuits; my thanks also to my brother and sister-in-law. The unflinching moral support at home helped me stay focused on my work.

# PUBLICATIONS BASED ON THIS THESIS

- 1. Somashekaracharya G. Bhaskaracharya, Uday Bondhugula, *PolyGLoT: A Polyhedral Loop Transformation Framework for a Graphical Dataflow Language*, International conference on Compiler Construction (CC 2013), Rome, Italy, pages 123 143, March 2013.

- 2. Somashekaracharya G. Bhaskaracharya, Uday Bondhugula, Albert Cohen, *Automatic Storage Optimization for Arrays*, ACM Transactions on Programming Languages and Systems (TOPLAS), vol 38, issue 3, pages 11:1–11:23, April 2016.

- 3. Somashekaracharya G. Bhaskaracharya, Uday Bondhugula, Albert Cohen, *SMO: An Integrated Approach to Intra-Array and Inter-Array Storage Optimization*, ACM SIGPLAN-SIGACT Symposium on Principles of Programming Languages (POPL), St.Petersberg, USA, pages 526 538, Jan 2016.

### **ABSTRACT**

Efficient memory usage is crucial for data-intensive applications as a smaller memory footprint ensures better cache performance and allows one to run a larger problem size given a fixed amount of main memory. The solutions found by existing techniques for automatic storage optimization for arrays in affine loop-nests, which minimize the storage requirements for the arrays, are often far from good or optimal and could even miss nearly all storage optimization potential. In this work, we present a new automatic storage optimization framework and techniques that can be used to achieve intra-array as well as inter-array storage reuse within affine loop-nests with a pre-determined schedule.

Over the last two decades, several heuristics have been developed for achieving complex transformations of affine loop-nests using the polyhedral model. However, there are no comparably strong heuristics for tackling the problem of automatic memory footprint optimization. We tackle the problem of storage optimization for arrays by formulating it as one of finding the right storage partitioning hyperplanes: each storage partition corresponds to a single storage location. Statement-wise storage partitioning hyperplanes are determined that partition a unified global array space so that values with overlapping live ranges are not mapped to the same partition. Our integrated heuristic for exploiting intra-array as well as inter-array reuse opportunities is driven by a fourfold objective function that not only minimizes the dimensionality and storage requirements of arrays required

for each high-level statement, but also maximizes inter-statement storage reuse.

We built an automatic polyhedral storage optimizer called SMO using our storage partitioning approach. Storage reduction factors and other results that we obtained from SMO demonstrate the effectiveness of our approach on several benchmarks drawn from the domains of image processing, stencil computations, high-performance computing, and the class of tiled codes in general. The reductions in storage requirement over previous approaches range from a constant factor to asymptotic in the loop blocking factor or array extents – the latter being a dramatic improvement for practical purposes.

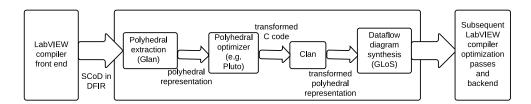

As an incidental and related topic, we also studied the problem of polyhedral compilation of graphical dataflow programs. While polyhedral techniques for program transformation are now used in several proprietary and open source compilers, most of the research on polyhedral compilation has focused on imperative languages such as C, where the computation is specified in terms of statements with zero or more nested loops and other control structures around them. Graphical dataflow languages, where there is no notion of statements or a schedule specifying their relative execution order, have so far not been studied using a powerful transformation or optimization approach. The execution semantics and referential transparency of dataflow languages impose a different set of challenges. In this work, we attempt to bridge this gap by presenting techniques that can be used to extract polyhedral representation from dataflow programs and to synthesize them from their equivalent polyhedral representation. We then describe PolyGLoT, a framework for automatic transformation of dataflow programs that we built using our techniques and other popular research tools such as Clan and Pluto. For the purpose of experimental evaluation, we used our tools to compile LabVIEW, one of the most widely used dataflow programming languages. Results show that dataflow programs transformed using our framework are able to outperform those compiled otherwise by up to a factor of seventeen, with a mean speed-up of 2.30× while running on an 8-core Intel system.

# CONTENTS

| AC | жпоч   | vieugements                                         | ]  |

|----|--------|-----------------------------------------------------|----|

| Pι | ıblica | tions based on this Thesis                          | ii |

| Ał | ostrac | et                                                  | v  |

| 1  | Intr   | oduction                                            | 1  |

|    | 1.1    | Automatic Storage Optimization                      | 1  |

|    | 1.2    | Polyhedral Compilation of Dataflow Programs         | 8  |

| 2  | Bac    | kground                                             | 11 |

|    | 2.1    | Affine Hyperplane                                   | 11 |

|    | 2.2    | Polyhedral Model                                    | 11 |

|    |        | 2.2.1 Overview of the Polyhedral Model              | 11 |

|    | 2.3    | Farkas' Lemma                                       | 13 |

|    | 2.4    | Successive Modulo Technique                         | 14 |

|    | 2.5    | Rectangular Hull for Inter-Array Reuse              | 15 |

|    | 2.6    | LabVIEW – Language and Compiler                     | 15 |

|    | 2.7    | An Abstract Model of Dataflow Programs              | 17 |

|    |        | 2.7.1 Inplaceness                                   | 19 |

| 3  | Intr   | a-Array Storage Optimization                        | 21 |

|    | 3.1    | A Simple Example                                    | 21 |

|    | 3.2    | Storage Hyperplanes and Conflict Satisfaction       | 24 |

|    | 3.3    | A Partitioning Approach                             | 25 |

|    |        | 3.3.1 Conflict Set Specification                    | 25 |

|    | 3.4    | Finding a Storage Hyperplane                        | 26 |

|    |        | 3.4.1 Encoding Satisfaction with Decision Variables | 27 |

|    |        | 3.4.2 Linearizing the Constraints                   | 29 |

viii CONTENTS

|   |      | 3.4.3 A Greedy Double-Objective               | 30 |

|---|------|-----------------------------------------------|----|

|   | 3.5  | Finding Storage Hyperplanes Iteratively       | 31 |

|   |      | 3.5.1 Example Revisited                       | 34 |

|   |      | 3.5.2 Correctness and Termination             | 34 |

|   | 3.6  | Optimality                                    | 35 |

|   | 3.7  | Examples                                      | 36 |

|   |      | 3.7.1 Blur Filter - Interleaved Schedule      | 36 |

|   |      | 3.7.2 Blur filter - Tiled Execution           | 38 |

|   |      | 3.7.3 Lattice-Boltzmann Method (LBM)          | 40 |

|   |      | 3.7.4 Diamond Tiling                          | 41 |

|   | 3.8  | Enumerating Storage Mappings                  | 43 |

|   |      | 3.8.1 Alternative Storage Hyperplanes         | 44 |

|   |      | 3.8.2 Diamond Tiling Revisited                | 48 |

|   | 3.9  | Related Work                                  | 49 |

| 4 | An I | ntegrated Approach to Storage Optimization    | 53 |

|   | 4.1  | A Simple Example                              | 53 |

|   |      | 4.1.1 Successive Modulo + Rectangular Hull    | 56 |

|   | 4.2  | A Global Array Space                          | 57 |

|   | 4.3  | Conflict Satisfaction in a Global Array Space | 58 |

|   | 4.4  | A Global Array Space Partitioning Approach    | 60 |

|   |      | 4.4.1 Global Conflict Set Specification       | 61 |

|   | 4.5  | Finding Storage Hyperplanes                   | 61 |

|   |      | 4.5.1 Analyzing Intra-Statement Conflicts     | 62 |

|   |      | , 6                                           | 63 |

|   |      | , ,                                           | 64 |

|   |      | 0 0 11 1                                      | 67 |

|   |      | •                                             | 70 |

|   |      | •                                             | 70 |

|   | 4.6  | •                                             | 73 |

|   |      |                                               | 74 |

|   |      | 0                                             | 76 |

|   | 4.7  |                                               | 79 |

|   | 4.8  | Related Work                                  | 81 |

| 5 | SMC  | ) - A Polyhedral Storage Optimizer            | 83 |

|   | 5.1  |                                               | 88 |

|   |      | 1                                             | 89 |

|   | 5.2  |                                               | 93 |

|   | 5.3  | Storage Mappings Using Enumerative Heuristic  | 96 |

CONTENTS ix

| 6   | Poly           | hedral Compilation Of A Graphical Dataflow Language | 101 |  |

|-----|----------------|-----------------------------------------------------|-----|--|

|     | 6.1            | Extracting the Polyhedral Representation            | 101 |  |

|     |                | 6.1.1 Challenges                                    | 102 |  |

|     |                | 6.1.2 Static Control Dataflow Diagram (SCoD)        | 103 |  |

|     |                | 6.1.3 A multi-dimensional schedule of compute-dags  | 106 |  |

|     | 6.2            | Code Synthesis                                      | 111 |  |

|     |                | 6.2.1 Input                                         | 111 |  |

|     |                | 6.2.2 Synthesizing a Dataflow Diagram               | 111 |  |

|     | 6.3            | The PolyGLoT Auto-Transformation Framework          | 118 |  |

|     | 6.4            | Experimental Evaluation                             | 119 |  |

|     | 6.5            | Related Work                                        | 121 |  |

| 7   | Con            | clusions                                            | 125 |  |

| Bil | ibliography 1: |                                                     |     |  |

# LIST OF TABLES

| 5.1  | baseline successive modulo technique ( [LF98]) with <i>B</i> being the loop block-                                                                          | 0.4 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2  | ing factor                                                                                                                                                  | 84  |

| 5.4  | Performance of various benchmarks with the storage mappings shown in Table 5.1                                                                              | 85  |

| 5.3  | Analysis of the performance of various benchmarks (shown in Table 5.2)                                                                                      | 00  |

|      | using VTune                                                                                                                                                 | 86  |

| 5.4  | Analysis of the performance of various benchmarks (shown in Table 5.2)                                                                                      |     |

|      | using VTune (continued from Table 5.3)                                                                                                                      | 87  |

| 5.5  | Execution time of multiple instances of LBMD2Q9 being run in a multipro-                                                                                    | 01  |

| 5.6  | grammed fashion                                                                                                                                             | 91  |

| 3.0  | grammed fashion                                                                                                                                             | 92  |

| 5.7  | Benchmark performance with the storage mappings of Table 5.8                                                                                                | 94  |

| 5.8  | Storage reduction obtained using our approach (SMO) compared to the                                                                                         |     |

|      | baseline (successive modulo [LF98] followed by rectangular hull), where B                                                                                   |     |

|      | is the loop blocking factor                                                                                                                                 | 95  |

| 5.9  | Various modulo storage mappings enumerated using Algorithm 2 compared                                                                                       | 0.0 |

| 5 1N | to the baseline (successive modulo [LF98], where <i>B</i> is the loop blocking factor Various modulo storage mappings enumerated using Algorithm 2 compared | 98  |

| 3.10 | to the baseline (successive modulo [LF98], where <i>B</i> is the loop blocking factor                                                                       | 99  |

| 6.1  | Summary of performance (sequential and parallel execution on an 8-core machine)                                                                             | 120 |

|      | macmine)                                                                                                                                                    | 120 |

# LIST OF FIGURES

| 1.1 | Storage requirement for the outlined file (of size $I$ ) can be reduced to $2I - 1$ .                                                                                                                                                                                  | 3  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | A stencil using a ping-pong buffer                                                                                                                                                                                                                                     | 5  |

| 1.3 | Storage optimization of ping-pong style 1-d stencil (from 2N to N+1) $\dots$                                                                                                                                                                                           | 6  |

| 2.1 | Polyhedral representation of a loop nest in geometric and linear algebraic form                                                                                                                                                                                        | 12 |

| 2.2 | Example of input code, the corresponding original schedule, a new schedule and transformed code.                                                                                                                                                                       | 12 |

| 2.3 | matmul in LabVIEW                                                                                                                                                                                                                                                      | 16 |

| 2.4 | DAG of the top-level diagram of <i>matmul</i>                                                                                                                                                                                                                          | 18 |

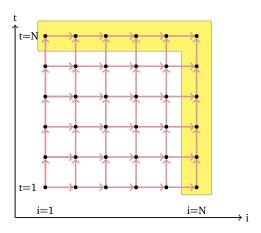

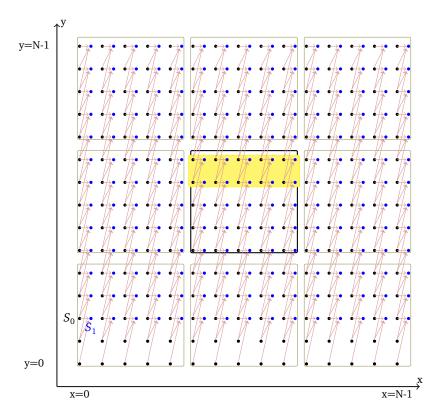

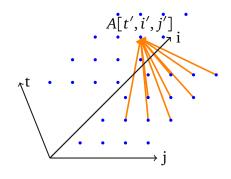

| 3.1 | The geometrical representation in Figure 3.1(d) shows the array space $A$ written to by statement $S$ in the code snippet shown in Figure 3.1(a). The red double-headed arrows in Figure 3.1(d) denote the various conflicts associated with the array index $(t',i')$ | 22 |

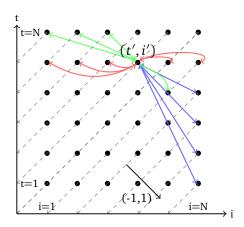

| 3.2 | Storage hyperplane $(-1,1)$ satisfies all conflicts                                                                                                                                                                                                                    | 34 |

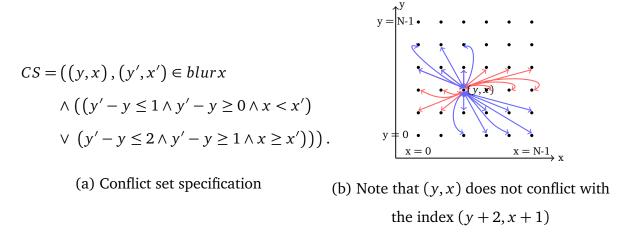

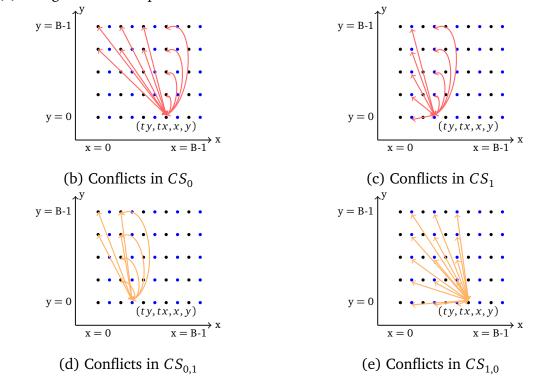

| 3.3 | Different versions of 2-stage blur filter                                                                                                                                                                                                                              | 37 |

| 3.4 | Blur filter (interleaved schedule) – set of conflicts associated with index                                                                                                                                                                                            |    |

|     | (y,x) and their geometrical representation                                                                                                                                                                                                                             | 37 |

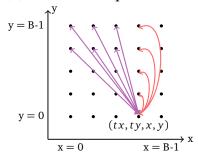

| 3.5 | Tiled execution of blur filter: $tx$ and $ty$ are the tile iterators whereas $x$ and $y$ are the intra-tile iterators. $B$ is the tile size                                                                                                                            | 38 |

| 3.6 | Blur filter (tiled execution) – conflict sets and their geometrical representa-                                                                                                                                                                                        |    |

|     | tion                                                                                                                                                                                                                                                                   | 39 |

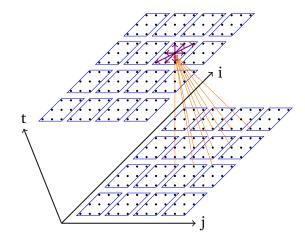

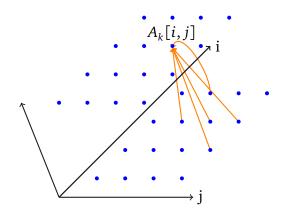

| 3.7 | As in a stencil, node $A[t', i', j']$ , in Figure 3.7(b), depends on neighboring                                                                                                                                                                                       |    |

|     | nodes from the previous time step                                                                                                                                                                                                                                      | 41 |

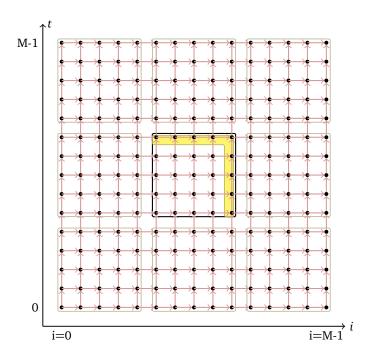

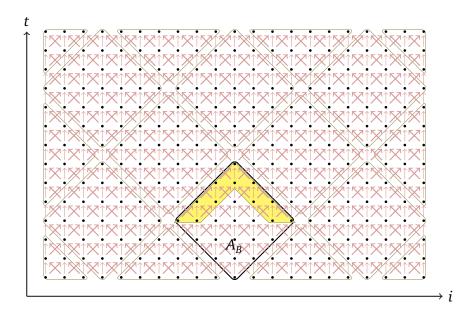

| 3.8 | $A_B$ is the data tile written to by iterations within the tile outlined in black.                                                                                                                                                                                     |    |

|     | Live-out data in yellow.                                                                                                                                                                                                                                               | 42 |

| 3.9 | Diamond tiling – conflict set and its geometric representation                                                                                                                                                                                                         | 43 |

xiv LIST OF FIGURES

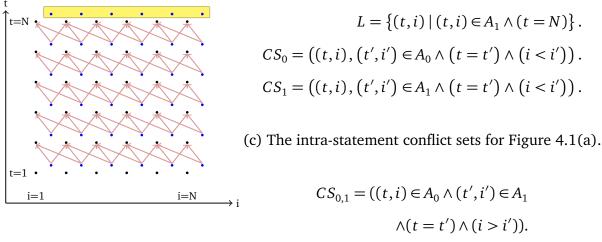

| 4.1 | Inter-statement and intra-statement conflict sets for 1-d ping-pong style                   |     |

|-----|---------------------------------------------------------------------------------------------|-----|

|     | stencil 1.2                                                                                 | 54  |

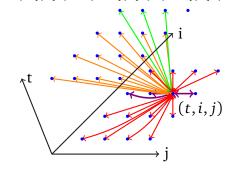

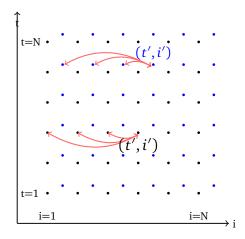

| 4.2 | The red arrows denote the intra-statement conflicts (see Figure 4.1(c))                     | 55  |

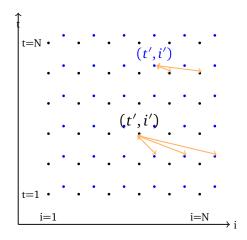

| 4.3 | The orange arrows denote inter-statement conflicts (cf. Figure 4.1(d))                      | 57  |

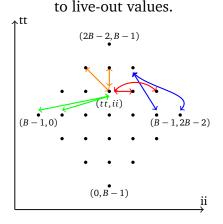

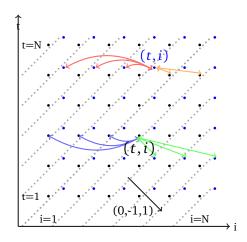

| 4.4 | Storage hyperplane $(0, -1, 1)$ satisfies all conflicts                                     | 73  |

| 4.5 | The conflict sets representing the intra-tile conflicts $(j, x, y) \bowtie (j', x', y')$ in |     |

|     | the global array space $A$ are shown in Figure 4.5(a). Statements $S_0$ and $S_1$           |     |

|     | write to the data tiles $A_{0T}$ and $A_{1T}$ respectively                                  | 75  |

| 4.6 | Smoothing in multi-grid methods using the Jacobi 2-d stencil                                | 77  |

| 4.7 | Storage optimization of Jacobi 2-d smoothing in multi-grid methods                          | 78  |

| 4.8 | Storage mappings obtained for Jacobi 2-d smoothing (refer Figure 4.7)                       | 79  |

| 6.1 | Single-element arrays and contradiction in schedule of compute-dags                         | 107 |

|     |                                                                                             |     |

| 6.2 | A high-level overview of PolyGLoT                                                           | 118 |

# **CHAPTER 1**

# INTRODUCTION

Efficient storage management for array variables in a program requires that memory locations be reused as much as possible, thereby minimizing their storage requirement. Consider a statement, which writes to an array, appearing within an arbitrarily nested loop. Two dynamic instances of the statement can store values that they compute to the same memory location provided the lifetimes of these values do not overlap. Therefore, most solutions to this problem are schedule-dependent. Storage optimization can be performed soon after execution reordering transformations have been applied, but before generating the final transformed code.

#### 1.1 Automatic Storage Optimization

Automatic techniques that reduce the storage requirements are quite crucial for dataintensive applications. In several cases, a programmer is particularly interested in running a dataset while utilizing the entire main memory capacity of a system. In such cases, performance (execution time) is secondary. Storage optimization allows a programmer to run a larger problem size for a given main memory capacity. When using multiple applications, 2 1. Introduction

it also allows more applications to fit in memory. In addition, storage optimization can also potentially improve performance as a direct result of a smaller memory footprint. It has also proved to be a critical optimization for domain-specific compilers. Image processing pipelines [RKBA<sup>+</sup>13] and stencil computations are two example domains where code generators rely on analysis to reduce the peak memory usage of the generated code. Compilers for functional languages with arrays, or dataflow languages with single-assignment semantics also need copy-avoidance to maximize memory reuse [AMMB<sup>+</sup>09].

The scope of programs that we consider for this work is a class of codes known as affine loop nests. Affine loop nests are sequences of arbitrarily nested loops (perfect or imperfect) where data accesses and loop bounds are affine functions of loop iterators and program parameters (symbols that do not vary within the loop nest). Due to the affine nature of data accesses, these loop program portions are statically predictable and can be analyzed and transformed using the polyhedral compiler framework [ASUL06]. Significant advances have been made in memory optimization for affine loop nests or its restricted forms [WR96, LF98, SCFS98, TVSA01, DSV05, ABD07]. However, we first show that a good memory optimization technique is still missing. The solutions found by existing works for several commonly encountered cases are far from good or optimal and could even miss nearly all storage optimization potential. Our method builds on the advances of the lattice-based memory contraction model [DSV05, ABD07], but approaches the problem in a new and very different way.

The storage optimization problem for arrays can be viewed as contracting the array along one or more dimensions to fixed sizes, or contracting along *directions* different from those along which the array is originally indexed. Thus, an approach to contraction can be viewed as one that finds: (1) good directions along which to contract (and the order in which to contract) in case the original ones are not good, and (2) the minimal sizes to which each of the chosen dimensions can be contracted. While the latter part was first comprehensively studied by Lefebvre and Feautrier [LF98], there is no heuristic available to obtain good solutions to the former. Choosing the right directions and their ordering impacts both the dimensionality of the resulting storage and the storage size. For example,

Figure 1.1: Storage requirement for the outlined tile (of size T) can be reduced to 2T - 1.

it can be the difference between say  $N^2$ , 2N, and N storage for what was originally an  $N \times N$  array. Earlier approaches [LF98, DSV05] had either worked with the canonical (original) basis or assumed that the right directions would be provided by an oracle.

Our scheme computes a storage allocation suitable for a given multi-dimensional schedule of the iterations. Typically, one determines a schedule based on criteria like locality, parallelism and potentially, even memory footprint. It is thus natural and reasonable to assume that the schedule has been fixed by the time storage contraction is ready to be performed. Our approach finds directions that minimize the dimensionality of the contracted storage. We introduce the notion of a *storage partitioning hyperplane*: such hyperplanes define a partitioning of the iteration space such that each partition uses a single memory location. Our approach is then of iteratively finding a minimum number of *storage partitioning hyperplanes* with certain criteria. The objectives ensure the right orientation of the storage hyperplanes such that the dimensionality of the contracted array is as low as possible, and for each of those dimensions, its extent is minimized.

4 1. Introduction

Consider the stencil computation with dependences (1,0), (0,1) in Figure 1.1. It corresponds to the tiled version of the code in Figure 3.1. For a given tile, only its top and right boundaries are live-out. As the primary objective behind tiling for locality is to exploit reuse in multiple directions while the data accessed fits in faster memory, live-out sets along two or more boundaries are common with tiling. In Figure 1.1, for a schedule that iterates row-wise within a tile, indexing the array along the canonical directions does not reduce storage, i.e., if T is the tile size,  $T^2$  storage per tile is needed. This solution corresponds to the canonical storage hyperplanes (1,0) and (0,1). The contraction factors obtained by Lefebvre and Feautrier [LF98] would just be N along each of the two dimensions. None of the heuristics described in [DSV05, ABD07] find a different basis. If the array is partitioned along the hyperplane (1,-1), i.e., if all points (t,i) in the array such that t - i = constant reuse the same memory location, the tile can be executed using a storage of just 2T-1 cells. The storage buffer would finally hold the 2T-1live-out values. An access A[t,i] will be transformed to an access  $A[(t-i) \mod (2T-1)]$ , and this is also the optimal solution. The occupancy vector based approach of Strout et al. [SCFS98] does obtain this optimal storage, but it is designed for perfect loop nests with constant dependences, and its schedule-independent nature leads to sub-optimal solutions in general. The schedule-dependent approach we develop in this paper finds the optimal storage mapping in this case automatically, and works for general affine loop nests. Other dependence patterns or more complex tiling shapes can lead to non-trivial mappings that are very difficult to derive by hand.

In addition to reuse opportunities across elements of a single array, there may also exist some scope for storage reuse or across multiple arrays. Intra-array storage management deals with how an array written to by a particular statement is compacted and accessed. On the other hand, inter-array reuse analysis pertains to memory locations from different arrays being written to in different high-level statements of a program. It might be possible to reduce the number of arrays to minimize the amount of allocated storage. Consider a high-level statement which writes to an array appearing within an arbitrarily nested loop. Multiple dynamic instances of the statement (arising out of an outer surrounding loop) can

store values that they compute to the same memory location provided the lifetimes of these values do not overlap. Besides general-purpose programming languages, storage optimization assumes high importance in domain-specific languages where high-level constructs provided to the programmer abstract away storage — providing the compiler with complete freedom in allocating and managing storage [AMMB+09, Lab10, RKBA+13, MVB15].

```

for (t=1; t<=N; t++){

for (i=1; i<=N; i++)

P[i] = f(Q[i-1],Q[i],Q[i+1]);

for (i=1; i<=N; i++)

Q[i] = P[i];

for (i=1; i<=N; i++)

result += Q[i];</pre>

```

Figure 1.2: A stencil using a ping-pong buffer

Consider the code in Figure 1.2. It uses two buffers P and Q in a ping-pong fashion so that the updated values are not immediately used in the same time (t) loop iteration. Such a pattern is common to several Jacobi-style smoothing operations used in iterative solution of partial differential equations, and in other stencil computations used in image processing. It is not obvious whether the total storage requirement of 2N (N for each of the two arrays) can be reduced any further, and developers of such code often assume that two arrays are needed. State-of-the-art intra-array storage optimization techniques and heuristics like that of Lefebvre and Feautrier [LF98], Darte et al. [DSV05] use modulo mappings to compact storage — the introduction of a modulo operator in the access expression leads to reuse of memory within the same array. In this case, if one analyzes intra-array lifetimes, no modulus smaller than N can be deduced. This effectively means no storage can be compacted. On the other hand, inter-array reuse techniques that analyze and capture the interference of lifetimes of different arrays are again unable to reuse storage between P and Q. This is because the lifetimes of both arrays are interleaved, and techniques like those based on graph coloring [LF98] or that of De Greef et al. [GCM97b] will be unable to reduce storage any further. Hence, no existing automatic intra-array or inter-array storage optimization technique can further optimize memory for the code in 6 1. Introduction

(a) Figure 1.2 with an optimized storage mapping

```

for (t=1; t<=N; t++)

for (i=1; i<=N; i++)

A[(i-t+N)%(N+1)] = f(A[(i-t+N)%(N+1)],

A[(i-t+1+N)%(N+1)],A[(i-t+2+N)%(N+1)]);

for (i=1; i<=N; i++)

result += A[i%(N+1)];</pre>

```

(b) After elimination of the dead code in Figure 1.3(a)

Figure 1.3: Storage optimization of ping-pong style 1-d stencil (from 2N to N+1)

Figure 1.2. However, a framework that takes an integrated and precise view of intra and inter-array memory reuse can indeed reduce storage from 2N to N+1. A mapping that enables this compaction is given by:

$$P_{t}[i] \rightarrow A[(i-t+N)\%(N+1)]$$

$Q_{t}[i] \rightarrow A[(i-t+N)\%(N+1)]$

where  $P_t[i]$  and  $Q_t[i]$  represent the values P[i] and Q[i] computed in iteration t of the outermost loop. Such a mapping leads to the code shown in Figure 1.3(a) with storage of just N+1 for array A. A surprising and positive side-effect of this mapping is that the second statement is turned into dead code! A subsequent compiler pass can completely eliminate the second statement (refer Figure 1.3(b)). This optimization opportunity is non-trivial to infer from the original code. Such a mapping not only leads to smaller storage, but also eliminates an unnecessary copy between the arrays while preserving semantics. The approach we present in this work is able to determine such mappings automatically. In the case of more realistic examples that employ 2-d or 3-d arrays, the

reduction is more prominent: from  $2N^2$  to  $N^2 + 2N$  for a code similar to Figure 1.2 that uses 2-d arrays, and from  $2N^3$  to about  $N^3 + 2N^2$  for one employing 3-d arrays. This allows a programmer to effectively process larger problems given a fixed amount of main memory available on a system, and use fewer physical nodes to solve a problem of a given size.

Our integrated approach for intra-array as well as inter-array storage optimization further builds on the notion of storage hyperplanes introduced earlier. Storage hyperplanes, in the context of inter-array storage optimization, have a meaning not just within an array but also across arrays. Often, programs intensive in data are written with arrays being produced as outputs while being consumed subsequently. The full extent of storage optimization can only be performed with a global view of conflicts. For example, the hyperplane that enables the storage optimization in Figure 1.3(a) is  $(i-t) = (-1,1) \cdot (t,i)^T$ . Our integrated approach to memory optimization subsumes previous intra-array optimization approaches while allowing effective inter-array optimization. The framework is also more powerful than an approach that decouples the two problems and solves them separately.

In essence, our contributions towards the problem of automatic storage optimization for arrays can be summarized as follows.

- We describe a new technique for storage optimization while casting the latter as an array space partitioning problem, where each partition uses a single memory location. We then formulate an ILP problem solvable using a greedy heuristic whose objective takes into account the dimensionality of the mapping as well as the extent along each dimension.

- We further develop an integrated approach to intra-statement as well as inter-statement storage optimization by generalizing the principle of storage partitioning for a unified global array space. We then present a greedy solution for finding statement-wise storage hyperplanes. The greedy objective is not only based on the dimensionality of the mapping and the extents along each dimension but also factors in the interstatement storage reuse considerations.

8 1. Introduction

We implement and evaluate our technique on various domain-specific benchmarks

and demonstrate reductions in storage requirement ranging from a constant factor

to asymptotic in the extents of the original array dimensions or loop blocking factors.

Finally, the techniques that we propose for storage optimization in affine loop-nests, by exploiting intra-array and inter-array reuse opportunities, have been built into SMO [SMO16], an open source tool which was developed as part of this work.

#### 1.2 Polyhedral Compilation of Dataflow Programs

As a somewhat related topic, we also study the problem of polyhedral compilation of dataflow programs. Many computationally intensive scientific and engineering applications that employ stencil computations, linear algebra operations, image processing kernels, etc. lend themselves to polyhedral compilation techniques [ASUL06, Bas]. Such computations exhibit certain properties that can be exploited at compile time to perform parallelization and data locality optimization.

Typically, the first stage of a polyhedral optimization framework consists of polyhedral extraction. Specific regions of the program that can be represented using the polyhedral model, typically affine loop nests, are analyzed. Such regions have been termed Static Control Parts (SCoPs) in the literature. Results of the analysis include an abstract mathematical representation of each statement in the SCoP, in terms of its iteration domain, schedule, and array accesses. Once dependences are analyzed, an automatic parallelization and locality optimization tool such as Pluto [Plu] is used to perform high-level optimizations. Finally, the transformed loop nests are synthesized using a loop generation tool such as CLooG [Bas04].

Regardless of whether an input program is written in an imperative language, a dataflow language, or using another paradigm, if a programmer does care about performance, it is important for the compiler not to ignore transformations that yield significant performance gains on modern architectures. These transformations include, for example, ones that enhance locality by optimizing for cache hierarchies and exploiting register reuse or those

that lead to effective coarse-grained parallelization on multiple cores. It is thus highly desirable to have techniques and abstractions that could bring the benefit of such transformations to all programming paradigms.

There are many compilers, both proprietary and open-source that now use the polyhedral compiler framework [GZA+11, MVW+11, BGDR10, Plu]. Research in this area, however, has predominantly focused on imperative languages such as C, C++, and Fortran. These tools rely on the fact that the code can be viewed as a sequence of statements executed one after the other. In contrast, a graphical dataflow program consists of an interconnected set of nodes that represent specific computations with data flowing along edges that connect the nodes, from one to another. There is no notion of a statement or a mutable storage allocation in such programs. Conceptually, the computation nodes can be viewed as consuming data flowing in to produce output data. Nodes become ready to be 'fired' as soon as data is available at all their inputs. The programs are thus inherently parallel. Furthermore, the transparency with respect to memory referencing allows such a program to write every output data value produced to a new memory location. Typically, however, copy avoidance strategies are employed to ensure that the output data is *inplace* to input data wherever possible. Such *inplaceness* decisions can in turn affect the execution schedule of the nodes.

The polyhedral extraction and code synthesis for dataflow programs, therefore, involves a different set of challenges to those for programs in an imperative language such as C. In this work, we propose techniques that address these issues. Furthermore, to demonstrate their practical relevance, we describe an automatic loop transformation framework that we built for the LabVIEW graphical dataflow programming language, which uses all of these techniques. Our contributions regarding the polyhedral compilation of graphical dataflow programs are as follows.

- We provide a specification of parts of a dataflow program that lends itself to the abstract mathematical representation of the polyhedral model.

- We describe a general approach for extracting the polyhedral representation for such a dataflow program part and also for the inverse process of code synthesis.

10 1. Introduction

• We present an experimental evaluation of our techniques for LabVIEW and comparison with the LabVIEW production compiler.

Chapter 2 provides the necessary background on the polyhedral model, the successive modulo technique of Lefebvre and Feautrier [LF98], a brief introduction to dataflow languages (LabVIEW, in particular) and introduces the notation used later. Chapters 3 and 4 present the details of our storage optimization scheme for exploiting intra-array and inter-array reuse respectively, along with related work and various examples drawn from real-world applications. Chapter 5 reports results obtained using an implementation of our automatic array optimization techniques. Most of the content in these three chapters has been published in [BBC16a] and [BBC16b]. Chapter 6 is based on our work published in [BB13]. It describes PolyGLoT, an auto-transformation framework for the LabVIEW graphical dataflow programming languages, and also provides a detailed discussion of the techniques that we developed to build this framework. An experimental evaluation of the same is reported in Section 6.4. Finally, our conclusions are presented in chapter 7.

# **CHAPTER 2**

# **BACKGROUND**

This chapter provides the background and notation required for the techniques that we describe in the later chapters for storage optimization and polyhedral compilation of dataflow programs.

### 2.1 Affine Hyperplane

**Definition 1.** The set of all vectors  $\vec{v} \in \mathbb{Z}^n$  such that  $\vec{h} \cdot \vec{v} = k$  constitute an affine hyperplane.

Different constant values for k generate different parallel instances of the hyperplane which is usually characterized by the vector,  $\vec{h}$ , normal to it.

#### 2.2 Polyhedral Model

#### 2.2.1 Overview of the Polyhedral Model

The polyhedral model provides an abstract mathematical model to reason about program transformations. Consider a program part that is a sequence of statements with zero or more loops surrounding each statement. The loops may be imperfectly nested. The

12 2. Background

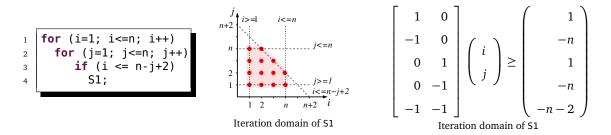

Figure 2.1: Polyhedral representation of a loop nest in geometric and linear algebraic form

```

for (i=1; i<=n-1; i++)</pre>

for (j=i+1; j<=n; j++)</pre>

\theta_{S1}(i,j) = (i,0,j,0)

/*S1*/ c[i][j] = a[j][i] / a[i][i];

for (j=i+1; j<=n; j++)

\theta_{S2}(i,j,k) = (i,1,j,k)

for (k=i+1; k<=n; k++)</pre>

5

/*S2*/ a[j][k] -= c[i][j] * a[i][k];

(b) Initial schedule

(a) Original code

for (t1=3; t1<=2*n-1; t1++)

for (t2=ceild(t1+1,2); t2<=min(n,t1-1); t2++)</pre>

\theta_{S_1}(i,j) = (i+j,j,0)

c[t1-t2][t2] = a[t2][t1-t2] / a[t1-t2][t1-t2];

for (t3=t1-t2+1; t3<=n; t3++)

\theta_{S_2}(i,j,k) = (i+j,j,1,k)

a[t2][t3] -= c[t1-t2][t2] * a[t1-t2][t3];

(c) New schedule

(d) Transformed code

```

Figure 2.2: Example of input code, the corresponding original schedule, a new schedule and transformed code.

dynamic instances of a statement S, are represented by the integer points of a polyhedron whose dimensions correspond to the enclosing loops. The set of dynamic instances of a statement is called its *iteration domain*, D. It is represented by the polyhedron, defined by a conjunction of affine inequalities that involve the enclosing loop iterators and global parameters. Each dynamic instance is uniquely identified by its *iteration vector*, i.e., the vector  $\vec{i}_S$  of enclosing loop iterator values. Figure 2.1 shows the polyhedral representation of a loop nest in its geometric and linear algebraic form.

**Schedules.** Each statement, or more precisely its domain, has an associated schedule, which is a multi-dimensional affine function mapping each integer point in the statement's domain to a unique time point that determines when it is to be executed. Code generated from the polyhedral representation scans integer points corresponding to all statements

2.3. Farkas' Lemma

globally in the lexicographic order of the time points they are mapped to. For example,  $\theta_S(i,j,k) = (i+j,j,k)$  is a schedule for a 3-d loop nest with original loop indices i,j,k. Changing the schedule to (i+j,k,j) would interchange the two inner loops. Figure 2.2 shows a code, its schedule as extracted from the input program, a new schedule and code generated with the new schedule. The new schedule fuses the j loops of both the statements while skewing the outermost loop with respect to the second outermost one. The reader is referred to [Bas] for more details on the polyhedral representation.

The initial schedule that is extracted, corresponding to the original execution order, is referred to as an *identity schedule*, i.e., if it is not modified, code generation will lead to the same code as the one from which the representation was extracted. A dimension of the multi-dimensional affine scheduling function is called a *scalar dimension* if it is a constant. In Figure 2.2(b), the second dimension of both statements' schedules are scalar dimensions. In the schedules listed in Figure 2.2(c), the third dimension is a scalar one. Polyhedral optimizers have models to pick a suitable schedule among valid ones. A commonly used model that minimizes dependence distances in the transformed space [BBK+08], thereby optimizing locality and parallelism simultaneously, is implemented in Pluto [Plu].

#### 2.3 Farkas' Lemma

Several polyhedral techniques rely on the application of the affine form of the Farkas' lemma [Sch86, Fea92a].

**Lemma 1.** Let D be a non-empty polyhedron defined by s affine inequalities or faces:  $\vec{a}_k \cdot \vec{x} + b_k \ge 0$ ,  $1 \le k \le s$ . An affine form  $\psi(\vec{x})$  is non-negative everywhere in D iff it is a non-negative combination of the faces, i.e.,

$$\psi(\vec{x}) = \lambda_0 + \Sigma_{(k=1)}^{(k=s)} \lambda_k \left( \vec{a_k} \cdot \vec{x} + b_k \right), \lambda_k \ge 0.$$

(2.1)

The  $\lambda_k$ s are known as Farkas multipliers.

14 2. Background

#### 2.4 Successive Modulo Technique

Lefebvre and Feautrier [LF98] proposed a storage optimization technique which they referred to as partial data expansion. A given static control program is subjected to array dataflow analysis and then converted into functionally equivalent single-assignment code so that all the artificial dependences (output and anti) are eliminated. The translation to single-assignment code involves rewriting the program so that each statement S writes to its own distinct array space  $A_S$ , which has the same size and shape as that of the iteration domain of S. Without any loss of generality, if we assume that the loop indices are nonnegative, then  $\vec{i}_S$  writes to  $A_S[\vec{i}]$ . This process of expanding the array space is known as total data expansion. A schedule  $\theta$  is then determined for the single-assignment code.

In order to alleviate the considerable memory overhead incurred due to such total expansion, the array space is then contracted along the axes represented by the loop iterators. This *partial expansion* technique is based on the notion of the *utility span* of a value computed by a statement instance  $\vec{i}_S$  at time  $\theta(\vec{i}_S)$  to a memory cell C. It is defined to be the sub-segment of the schedule during which the memory cell C is live, i.e., the value stored at C still has a pending use. Suppose that the last pending use of the value in C occurs in iteration  $L(\vec{i}_S)$ , at logical time  $\theta(L(\vec{i}_S))$ . Any new output dependence that does not conflict with the flow dependence between  $\vec{i}_S$  and  $L(\vec{i}_S)$  corresponding to the time interval  $[\theta(\vec{i}_S), \theta(L(\vec{i}_S))]$ , is an output dependence that can be safely introduced.

**Definition 2.** Two array indices  $\vec{i}$ ,  $\vec{j}$  such that  $\vec{i} \neq \vec{j}$  conflict with each other and the conflict relation  $\vec{i} \bowtie \vec{j}$  is said to hold iff  $\theta(\vec{i}_S) \preceq \theta(L(\vec{j}_S))$  and  $\theta(\vec{j}_S) \preceq \theta(L(\vec{i}_S))$  i.e., iff the corresponding array elements are simultaneously live under the given schedule  $\theta$ .

The conflict set CS is the set of all pairs of conflicting indices. It can be specified as  $CS = \{(\vec{i}, \vec{j}) \mid \vec{i} \bowtie \vec{j}\}$ . In accordance with the above definition, the conflict relation  $\bowtie$  is symmetric and non-reflexive. Partial expansion is performed iteratively with each statement being considered once at every depth of the surrounding loop nest. The *contraction modulo*  $e_p$  (or expansion degree as Lefebvre and Feautrier [LF98] refer to it), along the axis of the array space which corresponds to the loop at depth p, is computed as follows.

Suppose DS is the set of differences of indices which conflict, i.e.,  $DS = \{\vec{i} - \vec{j} \mid \vec{i} \bowtie \vec{j}\}$ . Similarly, let  $DS_p = \{\vec{i} - \vec{j} \mid \vec{i} \bowtie \vec{j} \land \vec{i} \succ \vec{j} \land (i_x = j_x \forall x < p)\}$ . If  $\vec{b}$  is the lexicographic maximum of  $DS_p$ , the contraction modulo is given by  $e_p = b_p + 1$ , where  $b_p \hat{u}_p$  is the component of  $\vec{b}$  along the axis  $i_p$ , with  $\hat{u}_p$  representing the unit vector along the same axis. In essence, the contraction modulo  $e_p$  represents the degree of contraction along that axis. The final storage mapping is obtained by converting it into a modulo mapping so that the statement instance  $\vec{i}_S$  writes to  $A_S[\vec{i} \mod \vec{e}]$ , where  $\vec{e} = (e_0, e_1, \dots, e_{n-1})$ . This method to determine the contraction moduli will hereafter be referred to as the *successive modulo technique*.

#### 2.5 Rectangular Hull for Inter-Array Reuse

Lefebvre and Feautrier [LF98] also propose a graph coloring based approach for interarray reuse. In this approach, an interference graph is constructed where each node represents a statement. An edge between two nodes corresponding to the statements  $S_i$  and  $S_j$  implies that the two statements cannot write to the same data structure — the prescribed shared data structure is nothing but the rectangular hull of the arrays  $A_{S_i}$  and  $A_{S_j}$  contracted in accordance with the successive modulo technique. Such inter-array reuse is possible only if a value computed by the statement  $S_i$  is not overwritten prematurely, before its last use, by an execution instance of the statement  $S_j$  and vice versa. A greedy coloring algorithm can then be applied on such an interference graph to determine the statements that can write to such a shared data structure. Hereafter, we refer to this technique as the *rectangular hull method*.

# 2.6 LabVIEW – Language and Compiler

LabVIEW is a graphical, dataflow programming language from National Instruments Corporation (NI) that is used by scientists and engineers around the world. Typically, it is used for implementing control and measurement systems, and embedded applications.

2. Background

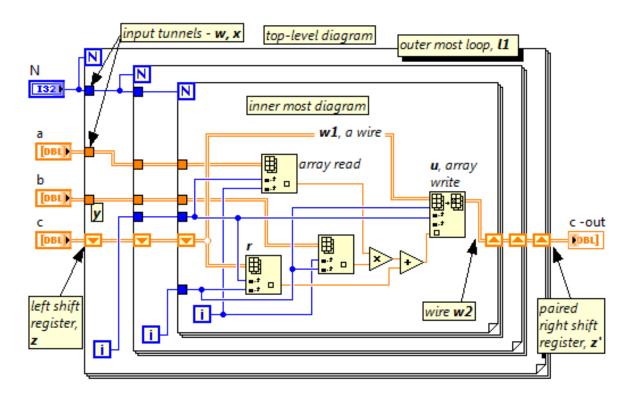

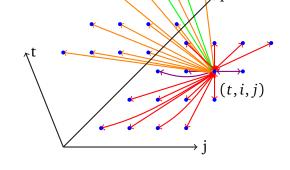

Figure 2.3: matmul in LabVIEW

The language itself, due to its graphical nature, is referred to as the G language. A Lab-VIEW program called a Virtual Instrument (VI) consists of a front panel (the graphical user interface) and a block diagram, which is the graphical dataflow diagram. Instead of textual statements, the program consists of specific computation nodes. The flow of data is represented by a *wire* that links the specific output on a source node to the specific input on a sink node.

The block diagram of a LabVIEW VI for matrix multiplication is shown in Figure 2.3. LabVIEW for-loops are unit-stride for-loops with zero-based indexing. A loop iterator node in the loop body (the [i] node) produces the index value in any iteration. A special node on the loop boundary (the N node) receives the upper loop bound value. The input arrays are provided by the nodes a, b and c. The output array is obtained at the node named c - out. The color of the wire indicates the type of data flowing along it e.g. blue for integers, orange for floats. Double lines are indicative of arrays.

Loop nodes act as special nodes that enclose the dataflow computation that is to be

executed in a loop. Data that is only read inside the loop flows through a special node on the boundary of the loop structure called the *input tunnel*. A pair of boundary nodes called the *left* and *right shift registers* are used to represent loop-carried dependence. Data flowing into the right shift register in one iteration flows out of the left shift register in the subsequent iteration. The data produced as a result of the entire loop computation flows out of the right shift register. Additionally, some boundary nodes are also used for the loop control. In addition to being inherently parallel because of the dataflow programming paradigm, LabVIEW also has a parallel for loop construct that can be used to parallelize the iterative computation [BDYF10].

The LabVIEW compiler first translates the G program into a Data Flow Intermediate Representation (DFIR) [Lab10]. It is a high-level, hierarchical and graph-based representation that closely corresponds to the G code. Likewise, we model the dataflow program as being conceptually organized in a hierarchy of diagrams. It is assumed that the diagrams are free of dead-code.

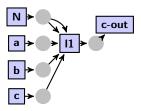

# 2.7 An Abstract Model of Dataflow Programs

Suppose N is the set of computation nodes and W is the set of wires in a particular diagram. Each diagram is associated with a directed acyclic graph (DAG), G = (V, E), where  $V = N \cup W$  and  $E = E_N \cup E_W$ .  $E_N \subseteq N \times W$  and  $E_W \subseteq W \times N$ . Essentially,  $E_N$  is the set of edges that connect the output of the computation nodes to the wires that will carry the output data. Likewise,  $E_W$  is the set of edges that connect the input of computation nodes to the wires that propagate the input data. We follow the convention of using small letters v and w to denote computation nodes and wires respectively. Any edge (v, w) represents a particular output of node v and any edge (w, v) represents a particular input of node v. So, the edges correspond to memory locations. The wires serve as copy nodes, if necessary. Figure 2.4 shows the DAG in the block diagram of the LabVIEW matrix multiplication program. In this abstract model, the gray nodes are wires. The 4 source nodes (N, a, b, c), the sink node (c-out) and the outermost loop are represented as the 6 blue nodes. Directed

18 2. Background

edges represent the connections from inputs/outputs of computation nodes to the wires, e.g. data from source node N flows over a wire into two inputs of the loop node. Hence the two directed edges from the corresponding wire node.

Figure 2.4: DAG of the top-level diagram of matmul.

For every  $n \in N$  that is a loop node, it is associated with a DAG,  $G_n = (V_n, E_n)$  which corresponds to the dataflow graph describing the loop body. The loop inputs and outputs are represented as source and sink vertices. The former have no incoming edges, whereas the latter have no outgoing edges. Let I and O be the set of inputs and outputs. Furthermore, a loop output vertex may be paired with a loop input vertex to signify a loop-carried data dependence i.e., data produced at the loop output in one iteration flows out of the input for the next iteration (Fig 2.3).

**Loop Inputs and Outputs.** Data flowing into and out of a loop is classified as either *loop-invariant input data* or *loop-carried data*. Loop-invariant input data is that which is only read in every iteration of the loop. Let Inv be the set of loop-invariant data inputs to the loop. The LabVIEW equivalent for such an input is an input tunnel. In Figure 2.3, for the outermost loop  $l_1$ ,  $Inv = \{w, x, y\}$ . Loop-carried data is that which is part of a loop-carried dependence inducing dataflow. The paired loop inputs and outputs represent such a dependence. Let ICar, OCar be sets of these loop inputs and outputs. The loop-carried dependence is represented by the one-to-one mapping  $lcd : OCar \rightarrow ICar$ . The LabVIEW equivalent for such a pair are the left and right shift registers. In Figure 2.3, for loop  $l_1, ICar = \{z\}, OCar = \{z'\}, (z, z') \in lcd$ .

### 2.7.1 Inplaceness

In accordance with the referential transparency of a dataflow program, each edge could correspond to a new memory location. Typically, however, a copy-avoidance strategy may be used to reuse memory locations. For example, consider the array element write node u in Figure 2.3, and its input and output wires,  $w_1$  and  $w_2$ . The output array data flowing along  $w_2$  could be stored in the same memory location as the input array data flowing along  $w_1$ . The output data can be *inplace* to the input data. The *can-inplace* relation  $(w_1, u) \leadsto (u, w_2)$  is said to hold.

In general, for any two edges (x,y) and  $(y,z),(x,y) \rightsquigarrow (y,z)$  holds iff the data inputs or outputs that these edges correspond to can share the same memory location (regardless of whether a specific copy-avoidance strategy chooses to reuse the memory location or not). The can-inplace relation is an equivalence relation. A path  $\{x_1, x_2, \ldots, x_n\}$  in a graph G = (V, E), such that  $(x_{i-1}, x_i) \rightsquigarrow (x_i, x_{i+1})$  for all  $2 \le i \le n-1$ , is said to be a can-inplace path. Note that by definition, the can-inplace relation  $(w_1, v) \rightsquigarrow (v, w_2)$  implies that the node v can overwrite the data flowing over  $w_1$ . In such a case, we say that the relation  $v \times w_1$  holds. However, the can-inplace relation  $(v_1, w) \rightsquigarrow (w, v_2)$  does not necessarily imply such a destructive operation as the purpose of a wire is to propagate data, not to modify it.

Suppose  $<_s$  is a binary relation on V which specifies a total ordering of the computation nodes. The relation  $<_s$  specifies a valid execution schedule iff  $(v_1 <_s v_2)$  implies that there does not exist a directed path in graph G, from  $v_2$  to  $v_1$  for any  $v_1, v_2 \in V$  i.e., the schedule respects all dataflow dependences. As we shall see later, the problem of scheduling the computation nodes is closely related to inplaceness. Memory reuse due to copy-avoidance can create additional dependences. A conjunction of scheduling relations  $\bigwedge(v_1 <_s v_2)$  is said to be *consistent* with a conjunction of can-inplace relations  $\bigwedge((x,y) \rightsquigarrow (y,z))$ , for  $x,y,z \in N \cup V$ , iff such a schedule does not violate the dependences imposed by such an inplaceness choice.

2. Background

**Array Accesses.** In Figure 2.3, the array read access is a node that takes in an array and the access index values to produce the indexed array element value. The array write access, takes the same set of inputs and the value to be written to produce an array with the indexed element overwritten. We model the array read and write accesses similarly. Notice that the output array of an array write,  $\nu$ , need not be inplace to the input array flowing through a wire  $w_1$ . If it is, then the array write performs a destructive update and we represent that using the relation  $\nu \times w_1$ .

# **CHAPTER 3**

# INTRA-ARRAY STORAGE OPTIMIZATION

In this chapter, we present all the details of our storage partitioning approach for achieving intra-array storage optimization.

### 3.1 A Simple Example

The successive modulo technique, described in Section 2.4, is quite versatile, scalable and also parametric. However, the eventual modulo storage mapping obtained does not always lead to minimal storage requirements. Consider the static control loop nests in Figure 3.1(a). The producer loop nest is already in single-assignment form where each statement instance S(t,i) writes to its own distinct memory cell A[t,i] so that the array space A has the same size and shape as the iteration domain of statement S. Suppose the schedule determined is  $\theta(t,i) = (t,i)$ . There are some values computed by statement S which are live even after all its instances have been executed. These live-out values reside in the set of memory cells,  $\{(t,i) \mid (t,i) \in A \land (i=N) \lor (t=N)\}$ . As a result, the conflict set S is made up of conflicts not only due to the uniform lifetimes of the non-live-out values but also due to the non-uniform lifetimes of the live-out values. Specifically, the

```

1  // the producer loop

2  for (t=1; t<=N; i++)

3   for (i=1; i<=N; i++)

4  /*S*/ A[t,i] = A[t,i-1] + A[t-1,i];

5  // the consumer loop

6  for (i=1; i<=N; i++)

8  result = result + A[i,N] + A[N,i];</pre>

```

(a) Iteration domain of S is shown in Figure 3.1(b).

(b) The maroon arrows denote flow dependences. Live-out portion is in yellow.

(d) A geometrical representation of conflicts

Figure 3.1: The geometrical representation in Figure 3.1(d) shows the array space A written to by statement S in the code snippet shown in Figure 3.1(a). The red double-headed arrows in Figure 3.1(d) denote the various conflicts associated with the array index (t', i').

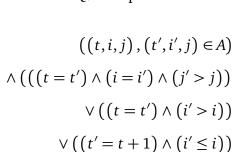

array index associated with a live-out value conflicts with the array index associated with any value computed later in the schedule. So, the resulting conflict set CS, of pairs of conflicting indices  $(t,i)\bowtie (t',i')$ , is a union of convex polyhedra characterized by the constraints shown in Figure 3.1(c).

The conflict relation is, strictly speaking, symmetric. For brevity, the constraints in

Figure 3.1(c) represent a conflict between a pair of conflicting indices only once, effectively treating it as an unordered pair. The first two disjuncts in Figure 3.1(c) together represent conflicts due to the flow dependence (1,0), which is also the maximum utility span of any non-live-out value (refer Figure 3.1(b)). The last disjunct expresses the conflicts due to the live-out values. The geometrical representation in Figure 3.1(d) shows the array space A written to by statement S in the code snippet shown in Figure 3.1(a). The red double-headed arrows in Figure 3.1(d) denote the various conflicts associated with the array index (t',i'). Please note that often, the last read of the value computed by one statement instance and the write by another instance of the same statement occur at the same logical time. Hereafter, in such scenarios, we do not treat the associated indices as conflicting since they can be mapped to the same memory cell e.g. in Figure 3.1(c), (t',i') and (t'+1,i') do not conflict.

Applying the successive modulo technique, at loop-depth p=0, the contraction modulo obtained is  $e_0=N$  due to the conflict  $(1,N)\bowtie (N,N)$ . Similarly, the contraction modulo at loop-depth p=1 is  $e_1=N$  due to the conflict  $(N,1)\bowtie (N,N)$ . The resulting modulo storage mapping of  $A[t,i]\to A[t\bmod N,i\bmod N]$  requires  $N^2$  storage.

A careful analysis reveals that a better storage mapping for the above example would be  $A[t,i] \rightarrow A[(i-t) \mod (2N-1)]$ . This mapping not only ensures that all the intermediate values computed are available until their last uses but also that the live-out values are available even after the producer loop has terminated. Furthermore, it drastically reduces the storage requirement from  $O(N^2)$  to O(N), requiring just a single row of 2N-1 cells. The above example shows that a straightforward computation of the contraction moduli along the canonical bases can lead to a solution which can be considerably worse than the optimal solution. As will be explained in the following sections, a better approach is to find hyperplanes which partition the array space based on the conflict set and to then use the hyperplane normals as the bases for computing the contraction moduli.

# 3.2 Storage Hyperplanes and Conflict Satisfaction

We formalize here the notion of a storage partitioning hyperplane (or storage hyperplane) satisfying a conflict  $\vec{i} \bowtie \vec{j}$  in the conflict set CS.

**Definition 3.** A conflict between a pair of array indices  $\vec{i}$  and  $\vec{j}$  is said to be satisfied by a hyperplane  $\vec{\Gamma}$  iff  $\vec{\Gamma} \cdot \vec{i} - \vec{\Gamma} \cdot \vec{j} \neq 0$ .

Essentially, if the hyperplane is thought of as partitioning the array space, a conflict is satisfied only if the array indices involved are mapped to different partitions.

The successive modulo technique can also be understood through this notion of conflict satisfaction. Consider again loop nest in Figure 3.1. As explained earlier, the contraction modulo  $e_0 = N$  is due to the conflict  $(1,N) \bowtie (N,N)$ . This is equivalent to the hyperplane (1,0) partitioning the array space into N partitions. Clearly, the conflicting indices (1,N) and (N,N) are mapped to different partitions, thus satisfying the conflict. The hyperplane (1,0) satisfies all the conflicts represented by the second and third disjuncts in Figure 3.1(c). The conflicts specified by the first disjunct are not satisfied as the conflicting indices get mapped to the same partition. However, these conflicts are satisfied at loop-depth p=1. This can be seen as the hyperplane (0,1) further partitioning each of the N partitions obtained earlier into N distinct sub-partitions. As a result, the conflicting indices in the conflicts that were not satisfied at the previous level get mapped to different partitions. In essence, the successive modulo approach can also be understood as conflict satisfaction being performed by successively partitioning the array space using a series of storage hyperplanes.

The dimensionality of the array space is a loose upper bound on the number of storage hyperplanes required to satisfy all the conflicts. This is because, in the trivial case, the hyperplanes could simply correspond to those which have the canonical axes as their normals. In fact, this is exactly how the modulo storage mapping is determined in the successive modulo technique. In Figure 3.1, all the conflicts were satisfied using the two canonical hyperplanes, (1,0), (0,1). However, the mapping  $A[t,i] \rightarrow A[(i-t) \mod (2N-1)]$ , which is better than the resulting solution not only in terms of the storage size required but

also in terms of its dimensionality, shows that it is possible to satisfy all the conflicts in the conflict set (Figure 3.1(c)) using just one storage hyperplane. Generally, the choice of partitioning hyperplanes affects both the dimensionality as well as the storage requirements of the resulting modulo storage mapping.

### 3.3 A Partitioning Approach

The problem of intra-array storage optimization for a given statement S with an n dimensional iteration domain D, writing to an array space A (of the same size and shape as D due to total data expansion), can be seen as a problem of finding a set of m partitioning hyperplanes  $\vec{\Gamma}_1, \vec{\Gamma}_2, \ldots, \vec{\Gamma}_m$ , which together satisfy all conflicts in the conflict set CS i.e., every conflict must be satisfied by at least one of the m hyperplanes. The resulting m-dimensional modulo storage mapping would be of the form  $A[\vec{i}] \to A[M\vec{i} \mod \vec{e}]$  where M is the  $m \times n$  transformation matrix constructed using the m storage hyperplanes as the m rows of the matrix. If a hyperplane is  $\Gamma_i = (\gamma_{i,1}, \gamma_{i,2}, \ldots, \gamma_{i,n})$ , then the storage mapping matrix M is an  $m \times n$  matrix with the  $i^{th}$  row  $(\gamma_{i,1}, \gamma_{i,2}, \ldots, \gamma_{i,n})$ .

The contraction moduli computed along the normals of the m hyperplanes form the m components of the vector  $\vec{e}$ .

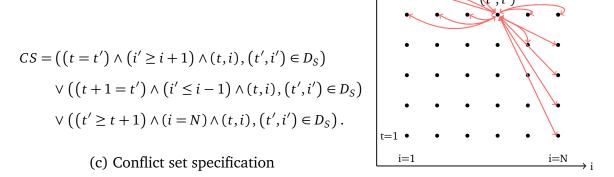

### 3.3.1 Conflict Set Specification

The conflict set can be specified as a union of convex polyhedra, also called *conflict polyhedra*, e.g., the disjunction in Figure 3.1(c). Each integer point in a conflict polyhedron represents a particular conflict. The symmetric property of the conflict relation can be

used to simplify the conflict set significantly. Consider a 1-d array space A where all array indices conflict with all other indices. The conflict set CS is then the set of ordered pairs (i, i') such that  $i \bowtie i'$  holds. A conflict relation  $1 \bowtie 2$  can be encoded as the integer point (1,2) in the conflict polyhedron  $\{i < i' \mid i,i' \in A\}$ . Strictly speaking though, if all conflict relations are to be represented, due to the symmetry, another conflict polyhedron  $\{i > i' \mid i, i' \in A\}$  would be required to accommodate the conflict relation  $2 \bowtie 1$ . However, satisfying the conflict  $1 \bowtie 2$  implies that  $2 \bowtie 1$  is also satisfied as both of them represent the same pair of indices. The second conflict polyhedron is, in effect, redundant in the conflict set. Hereafter, we assume that if a conflict relation  $\vec{i} \bowtie \vec{j}$  is represented in a conflict set CS, then CS does not contain a redundant representation of the relation  $\vec{i} \bowtie \vec{i}$  as well. There may be multiple ways to specify a conflict set as a union of conflict polyhedra. Therefore, we adhere to the convention that if the conflict relation  $\vec{i}\bowtie\vec{j}$  is represented in the conflict set, the value for the conflicting index  $\vec{j}$  must not be computed earlier than that for the index  $\vec{i}$  according to the given schedule. Furthermore, the conflict set specification is minimal in the sense that no two conflict polyhedra exist in the union such that their union is itself convex.

### 3.4 Finding a Storage Hyperplane

In the scenario when the conflict set is empty to begin with, the optimal allocation is to contract the array down to a single scalar variable. Storage hyperplanes only need to be found when the conflict set is non-empty. Suppose there are l conflict polyhedra  $K_1, K_2, \ldots, K_l$  so that the conflict set  $CS = \bigcup_{i=1}^{i=l} K_i$ . Consider a pair of conflicting indices  $\vec{s}$  and  $\vec{t}$ . By Definition 3, a hyperplane  $\vec{\Gamma}$  satisfies this conflict if  $(\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t}) \neq 0$ . This can be expressed by the disjunction:

$$\left(\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t}\right) \geq 1 \quad \lor \quad \left(\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t}\right) \leq -1.$$

Furthermore, since the iteration space D (and consequently, the array space A) is bounded, there must exist a finite upper bound of the form  $(\vec{u}.\vec{P}+w)$  on  $(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t})$ , where  $\vec{P}$  is the

vector of program parameters. Such a bound has been used in [Fea92a] and in [BBK<sup>+</sup>08], although in different contexts. Additionally, as the conflict relation is symmetric, the upper bound is applicable to the absolute value of the conflict difference  $(\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t})$ . So, the bounding constraints can be expressed as follows:

$$-\left(\vec{u}.\vec{P}+w\right) \leq \left(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t}\right) \leq \left(\vec{u}.\vec{P}+w\right). \tag{3.1}$$

#### 3.4.1 Encoding Satisfaction with Decision Variables

A storage hyperplane  $\vec{\Gamma}$  may not necessarily satisfy all conflicts in the conflict set CS. It may not even satisfy all the conflicts represented in a particular conflict polyhedron. So, in general,  $(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t})$  could be positive, negative, or equal to zero. This nature of conflict satisfaction can be captured adequately by introducing a pair of binary decision variables  $x_{1i}, x_{2i}$  for each conflict polyhedron  $K_i$  such that:

$$x_{1i} = \begin{cases} 1 & \text{if } (\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t}) \ge 1, \ \forall \ \vec{s} \bowtie \vec{t} \in K_i, \\ 0 & \text{if otherwise.} \end{cases}$$

$$x_{2i} = \begin{cases} 1 & \text{if } (\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t}) \le -1, \ \forall \ \vec{s} \bowtie \vec{t} \in K_i, \\ 0 & \text{if otherwise.} \end{cases}$$

Note that the binary decision variables  $x_{1i}$ ,  $x_{2i}$  indicate the nature of conflict satisfaction at the granularity level of a conflict polyhedron and not at the granularity level of each conflict. Even if there exists one conflict in the conflict polyhedron which is not satisfied by the hyperplane, then the conflict polyhedron, as a whole, is still treated as unsatisfied. So, the constraint that  $(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t})$  could be positive, negative, or equal to zero can be expressed as the conjunction:

$$\left(\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t}\right) \ge 1 - \left(1 - x_{1i}\right) \left(\vec{u}.\vec{P} + w + 1\right)$$

$$\wedge \quad \left(\vec{\Gamma}.\vec{s} - \vec{\Gamma}.\vec{t}\right) \le -1 + \left(1 - x_{2i}\right) \left(\vec{u}.\vec{P} + w + 1\right). \tag{3.2}$$

By definition,  $x_{1i}$  and  $x_{2i}$  cannot be simultaneously equal to 1. Such a scenario would mean that the constraints in the above conjunction would contradict each other. However, if  $x_{1i}=1$  and  $x_{2i}=0$ , then the first conjunct degenerates into the conflict satisfaction constraint  $(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t})\geq 1$  whereas the second conjunct is reduced to the constraint  $(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t})\leq (\vec{u}.\vec{P}+w)$ , which is implied by the bounding constraints (3.1). Similarly, if  $x_{2i}=1$  and  $x_{1i}=0$ , the first conjunct becomes  $(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t})\geq -(\vec{u}.\vec{P}+w)$  which is again implied by the bounding constraints (3.1). The second conjunct degenerates into the conflict satisfaction constraint  $(\vec{\Gamma}.\vec{s}-\vec{\Gamma}.\vec{t})\leq -1$ . When there is still at least one conflict which remains unsatisfied, both  $x_{1i}$  and  $x_{2i}$  must be equal to 0. In such a scenario, it can be seen that neither of the two conjuncts degenerate into a conflict satisfaction constraint. Instead, the entire conjunction boils down to the bounding constraints (3.1), which must always hold, regardless of whether all or a few of the conflicts in the conflict polyhedron are satisfied.

Each of the *l* conflict polyhedra is associated with its own pair of binary decision variables, both of which cannot simultaneously be equal to one. So, the number of conflict polyhedra all of whose conflicts are satisfied by a hyperplane can be estimated as the sum of all the decision variables:

$$\eta = \sum_{i=1}^{i=l} (x_{1i} + x_{2i}). \tag{3.3}$$

The number  $\eta$  forms the basis of our greedy heuristic for finding good storage hyperplanes. Greater the value of  $\eta$ , fewer the number of conflict polyhedra whose conflicts still remain unsatisfied. Consequently, it is likely that fewer storage hyperplanes will be needed to satisfy the remaining conflicts. A particularly interesting case is when  $\eta$  can be made to equal l. The storage hyperplane found then would have satisfied all conflicts on its own without the need to find any more hyperplanes. In other words, maximizing  $\eta$  serves as a reasonably good greedy approach for minimizing the number of storage hyperplanes and thereby, the dimensionality of the final storage mapping.

### 3.4.2 Linearizing the Constraints